160 AMD Geode™ LX Processors Data Book

CPU Core Register Descriptions

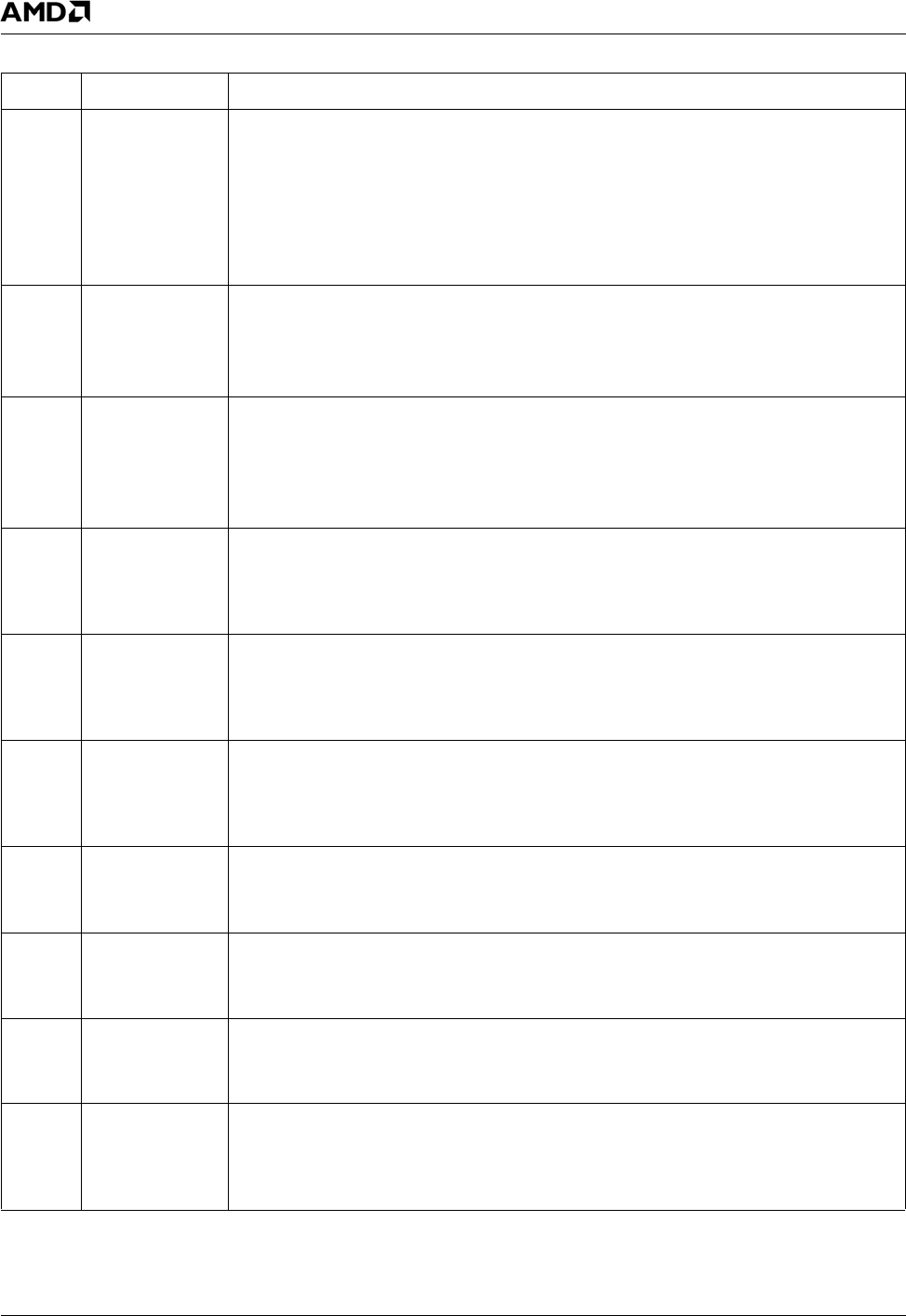

33234H

32 WBDIS Write Buffer Disable. Disabling the write buffer forces stores to be sent directly from the

output of the store queue to the bus controller. Enabling the write buffer allows memory

stores to be buffered, with or without combining based on region properties.

0: Enable write buffer. (Default)

1: Disable write buffer.

Note: If write allocate is used in any region configuration register, then the write buffer

must be enabled.

31:16 LSLOCK Load/Store Lockout. Bit mask of ways which cannot be allocated or replaced on a load

or store miss. If all ways are locked, caching is effectively disabled, though the cache will

still be interrogated. Use DCDIS (bit 8) to disable the interrogations as well. Note that this

field has been increased from 4 bits in the AMD Geode™ GX processor to 16 bits to

allow for the new 16 way cache). (Default = 0)

15 NOLOCKEVCT Do Not Evict Clean Lines Locked by LSLOCK. When this bit is 1, clean lines locked by

LSLOCK will not be evicted into the L2 cache upon replacement. This feature is intended

to be used with the auto-prefetch mechanism to prevent auto-prefetched data from get-

ting into the L2 cache. In this case, LSLOCK and APFLOCK would divide the ways of the

cache into prefetched and non-prefetched ways. Only the non-prefetched ways would be

evicted into the L2. (Default = 0)

14 EVCTONRPL Evict Clean Lines on Replacement. This bit should be set when an external L2 cache is

operating in Victim mode.

0: Invalidate clean cache lines when replaced, do not evict. (Default)

1: Evict clean cache lines when they are replaced.

13 NOFTTBRES No Page Fault. Do not page fault if any reserved bits are set in the Directory Table

Entries (DTE)/Page Table Entries (PTE).

0: Take the page fault. (Default)

1: Do not take the page fault.

12 DTCNINV Do Not Invalidate DTE Cache Entry. Do not invalidate DTE cache entry on INVLPG

instruction. Entire DTE cache is still flushed on a store into the directory page.

0: Invalidate DTE cache entry if INVLPG hits. (Default)

1: Do not invalidate DTE cache entry on INVLPG.

11 P4MDIS Disable 4M PTE Cache.

0: Allow 4M PTEs to be cached. (Default)

1: Do not cache 4M PTEs and flush any existing entries.

10 DTCDIS Disable DTE Cache.

0: Allow DTEs to be cached. (Default)

1: Do not cache DTEs, flush any existing entries.

9 L2TDIS Disable L2 TLB. Contents will not be modified.

0: Interrogate and allocate entries in the L2 TLB. (Default)

1: L2 TLB will always generate a miss.

8 DCDIS Disable Data Cache (completely). Contents will not be modified. Intended to be used

for array testing or in case of cache array failure.

0: Use standard x86 cacheability rules. (Default)

1: Data cache will always generate a miss.

DM_CONFIG0_MSR Bit Descriptions (Continued)

Bits Name Description