AMD Geode™ LX Processors Data Book 665

Instruction Set

33234H

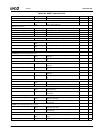

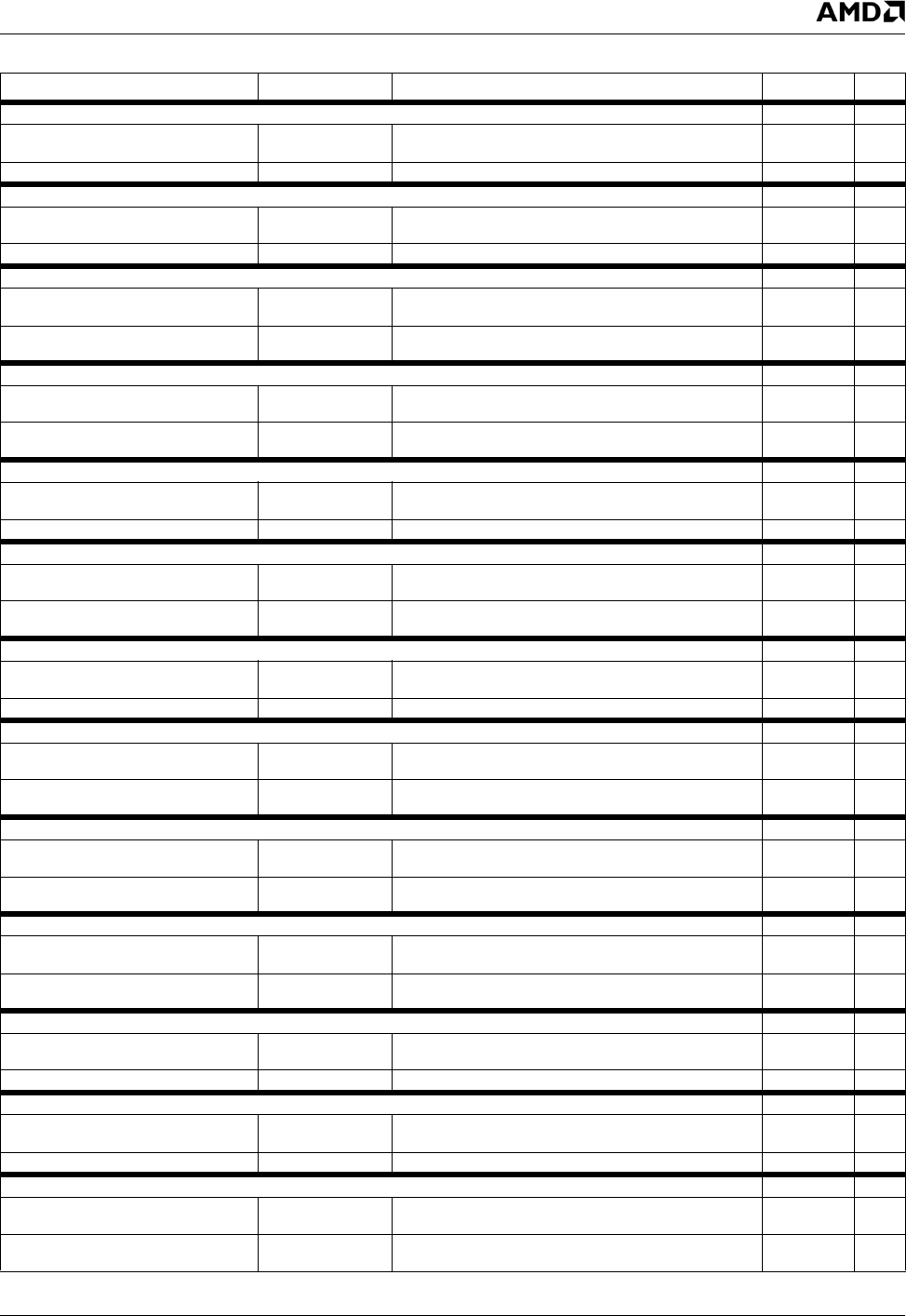

PSUBB Subtract Byte With Wrap-Around

MMX Register 2 to MMX Register 1 0FF8 [11 mm1

mm2]

MMX reg 1 [byte] <--- MMX reg 1 [byte] - MMX reg 2 [byte] 2

Memory to MMX Register 0FF8 [mod mm r/m] MMX reg [byte] <--- MMX reg [byte] - memory [byte] 2

PSUBD Subtract Dword With Wrap-Around

MMX Register 2 to MMX Register 1 0FFA [11 mm1

mm2]

MMX reg 1 [dword] <--- MMX reg 1 [dword] - MMX reg 2

[dword]

2

Memory to MMX Register 0FFA [mod mm r/m] MMX reg [dword] <--- MMX reg [dword] - memory64 [dword] 2

PSUBSB Subtract Byte Signed With Saturation

MMX Register 2 to MMX Register 1 0FE8 [11 mm1

mm2]

MMX reg 1 [sign byte] <--- sat -- (MMX reg 1 [sign byte] sub-

tract MMX reg 2 [sign byte])

2

Memory to MMX Register 0FE8 [mod mm r/m] MMX reg [sign byte] <--- sat --- (MMX reg [sign byte] subtract

memory64 [sign byte])

2

PSUBSW Subtract Word Signed With Saturation

MMX Register 2 to MMX Register 1 0FE9 [11 mm1

mm2]

MMX reg 1 [sign word] <--- sat --- (MMX reg 1 [sign word] -

MMX reg 2 [sign word])

2

Memory to MMX Register 0FE9 [mod mm r/m] MMX reg [sign word] <--- sat --- (MMX reg [sign word] -

memory64 [sign word])

2

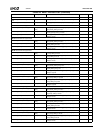

PSUBUSB Subtract Byte Unsigned With Saturation

MMX Register 2 to MMX Register 1 0FD8 [11 mm1

mm2]

MMX reg 1 [byte] <--- sat --- (MMX reg 1 [byte] - MMX reg 2

[byte])

2

Memory to MMX Register 0FD8 [11 mm reg] MMX reg [byte] <--- sat --- (MMX reg [byte] - memory64 [byte]) 2

PSUBUSW Subtract Word Unsigned With Saturation

MMX Register 2 to MMX Register 1 0FD9 [11 mm1

mm2]

MMX reg 1 [word] <--- sat --- (MMX reg 1 [word] - MMX reg 2

[word])

2

Memory to MMX Register 0FD9 [11 mm reg] MMX reg [word] <--- sat --- (MMX reg [word] - memory64

[word])

2

PSUBW Subtract Word With Wrap-Around

MMX Register 2 to MMX Register 1 0FF9 [11 mm1

mm2]

MMX reg 1 [word] <--- (MMX reg 1 [word] - MMX reg 2 [word]) 2

Memory to MMX Register 0FF9 [mod mm r/m] MMX reg [word] <--- (MMX reg [word] - memory64 [word]) 2

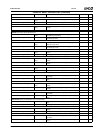

PUNPCKHBW Unpack High Packed Byte, Data to Packed Words

MMX Register 2 to MMX Register 1 0F68 [11 mm1 mm2] MMX reg 1 [word] <--- {MMX reg 1 [high byte], MMX reg 2

[high byte]}

2

Memory to MMX Register 0F68 [11 mm reg] MMX reg [word] <--- {memory64 [high byte], MMX reg [high

byte]}

2

PUNPCKHDQ Unpack High Packed Dword, Data to Qword

MMX Register 2 to MMX Register 1 0F6A [11 mm1

mm2]

MMX reg 1 <--- MMX reg 1 [high dword], MMX reg 2 [high

dword]

2

Memory to MMX Register 0F6A [11 mm reg] MMX reg <--- {memory64 [high dword], MMX reg [high

dword]}

2

PUNPCKHWD Unpack High Packed Word, Data to Packed Dwords

MMX Register 2 to MMX Register 1 0F69 [11 mm1 mm2] MMX reg 1 [dword] <--- MMX reg 1 [high word], MMX reg 2

[high word]

2

Memory to MMX Register 0F69 [11 mm reg] MMX reg [dword] <--- memory64 [high word], MMX reg [high

word]

2

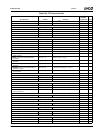

PUNPCKLBW Unpack Low Packed Byte, Data to Packed Words

MMX Register 2 to MMX Register 1 0F60 [11 mm1 mm2] MMX reg 1 [word] <--- MMX reg 1 [low byte], MMX reg 2 [low

byte]

2

Memory to MMX Register 0F60 [11 mm reg] MMX reg [word] <--- memory64 [low byte], MMX reg [low byte] 2

PUNPCKLDQ Unpack Low Packed Dword, Data to Qword

MMX Register 2 to MMX Register 1 0F62 [11 mm1 mm2] MMX reg 1 <--- MMX reg 1 [low dword], MMX reg 2 [low

dword]

2

Memory to MMX Register 0F62 [11 mm reg] MMX reg <--- memory64 [low dword], MMX reg [low dword] 2

PUNPCKLWD Unpack Low Packed Word, Data to Packed Dwords

MMX Register 2 to MMX Register 1 0F61 [11 mm1 mm2] MMX reg 1 [dword] <--- MMX reg 1 [low word], MMX reg 2

[low word]

2

Memory to MMX Register 0F61 [11 mm reg] MMX reg [dword] <--- memory64 [low word], MMX reg [low

word]

2

Table 8-28. MMX™ Instruction Set (Continued)

MMX™ Instructions Opcode Operation Clock Ct Notes