A-4

Cisco MGX 8800/8900 Series Hardware Installation Guide

Releases 2 - 5.2, Part Number OL-4545-01, Rev. H0, May 2006

Appendix

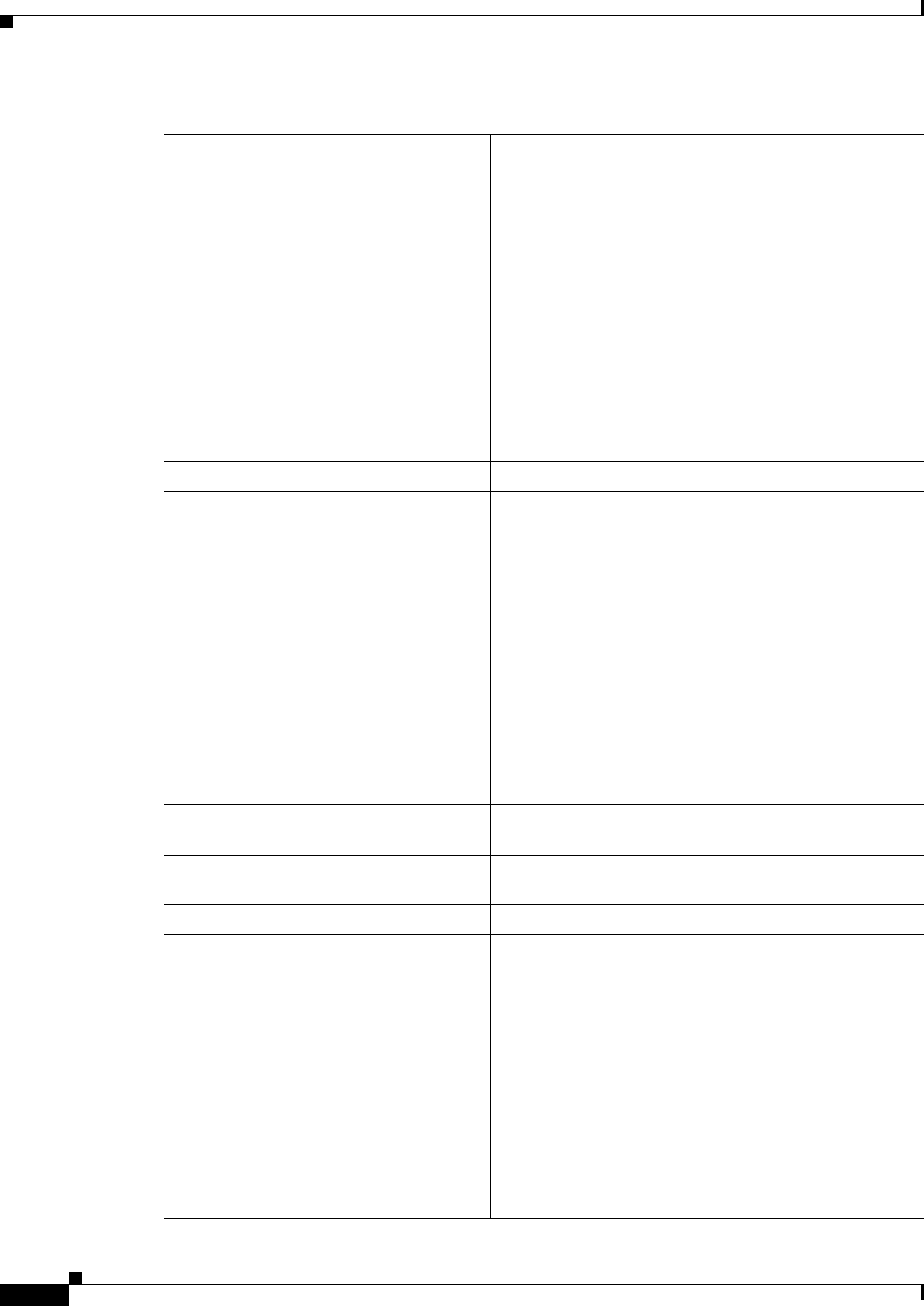

PXM1E Specifications

Processor clock speed and memory

specifics

Clock speed: 350 MHz internal, 100 MHz external

Flash memory: 2 MB

DRAM: 256 MB

Tertiary cache: 2 MB

External L3 cache: 2 MB

Secondary cache: 256 KB

BRAM

1

: 512 KB

DRAM: 256 MB

Hard disk: 6 to 20 GB

CPU: R7000

Maximum switch fabric throughput 1.2 Gbps

Control access

Note These ports exist on the user

interface back cards.

• Control port: RJ-45 receptacle, EIA/TIA-232, DTE

mode, asynchronous interface, 19,200 baud, 1 start

bit, 1 stop bit, no parity bits

• Maintenance port: RJ-45 receptacle, EIA/TIA-232,

DTE mode, asynchronous interface, 19,200 baud, 1

start bit, 1 stop bit, no parity bits

• LAN port: RJ-45 receptacle, 10BASE-T,

802.3 Ethernet

• Two serial ports for the following:

–

PNNI modem port

–

IOS control port

–

IOS modem port

Number of logical ports 32 logical ports across all physical ports on the NNI/UNI

port back card (regardless of line type)

Alarm indicators (audible and visual) Central office-compatible alarm indicators and controls

through a DB-15 receptacle

BITS

2

clock interface T1 and E1 with an RJ-48 receptacle

Stratum 3 synchronization (internal and

external)

• Free-run accuracy of ± 4.6 ppm (± 7 Hz at 1.544 MHz)

• Holdover stability of less than 255 slips (±.37 ppm)

for the initial 24 hours of holdover

• Upon clock switchover, MTIE

3

does not exceed 1

microsecond and rate of phase change does not

exceed 81 ns

4

in a 1.326-ms interval

• Pull-in range of accuracy ± 4.6 ppm

• Provides jitter filtering and tolerance according to

AT&T T1.5 and ITU G.824 specifications

• Declares a bad reference if LOS detected > 50 ms or

error burst of duration > 2.5 sec.

Table A-3 PXM1E Specifications (continued)

Specification Description