CHAPTER 2 V

R

4120A

102

Preliminary User’s Manual S15543EJ1V0UM

2.4.2 Virtual address space

This section describes the virtual/physical address space and the manner in which virtual addresses are converted

or “translated” into physical addresses in the TLB. The V

R

4120A virtual address can be either 32 or 64 bits wide,

depending on whether the processor is operating in 32-bit or 64-bit mode.

In 32-bit mode, addresses are 32 bits wide. The maximum user process size is 2 Gbytes (2

31

).

In 64-bit mode, addresses are 64 bits wide. The maximum user process size is 1 Tbyte (2

40

).

As shown in Figure 2-25, the virtual address is extended with an address space identifier (ASID), which reduces

the frequency of TLB flushing when switching contexts. This 8-bit ASID is in the CP0 EntryHi register, described later

in this chapter. The Global (G) bit is in the EntryLo0 and EntryLo1 registers, described later in this section.

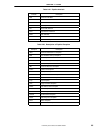

Figure 2-25. Virtual-to-Physical Address Translation

Virtual address

The offset is then added to the PFN

passing through the TLB.

If there is a match, the page frame

number (PFN) representing the high-

order bits of the physical address is

output from the TLB.

The virtual page number (VPN) in the

virtual address (VA) is compared with

the VPN in the TLB.

TLB

entry

Physical address

3

2

TLB

1

ASID OffsetVPN

Offset

PFN

PFN

G

ASID VPN