APPENDIX A MIPS III INSTRUCTION SET DETAILS

Preliminary User’s Manual S15543EJ1V0UM

501

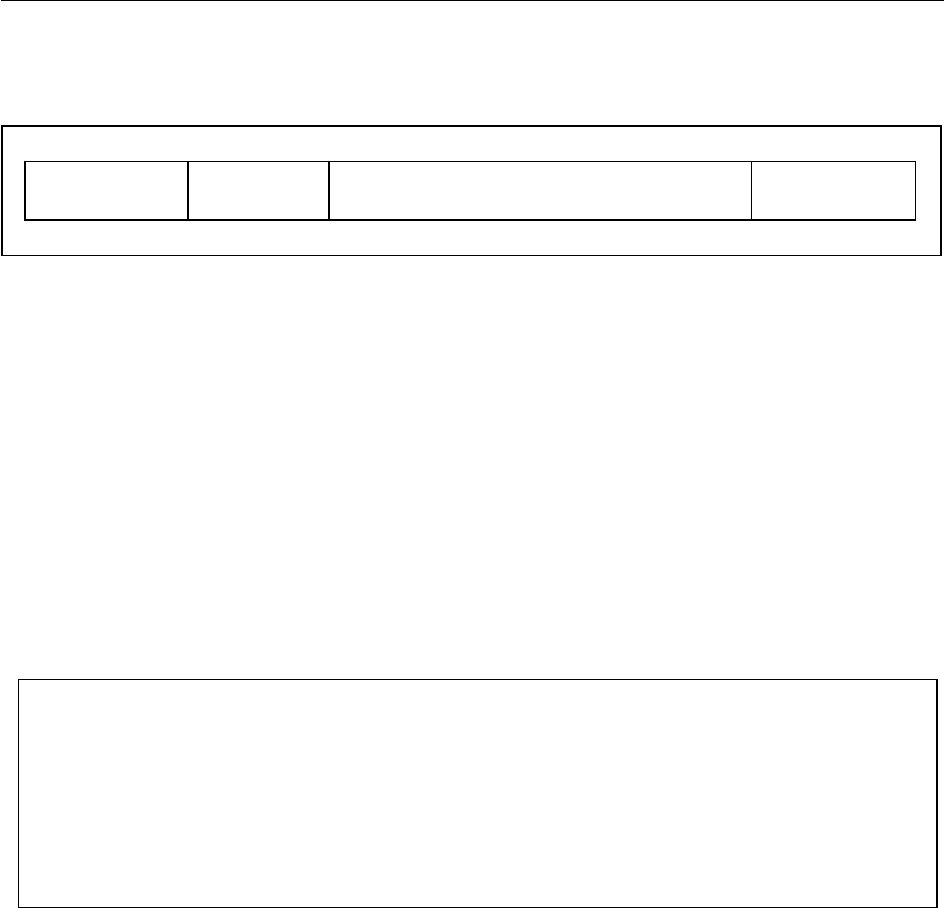

JR

Jump Register

JR

rs

SPECIAL

0 0 0 0 0 0

0

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

31 26 25 21 20 0

65 15

JR

0 0 1 0 0 0

65

6

Format:

JR rs

Description:

The program unconditionally jumps to the address contained in general register

rs

, with a delay of one instruction.

When a MIPS16 instruction can be executed, the program unconditionally jumps with a delay of one instruction to

the address indicated by the value of clearing the least significant bit of the general register

rs

to 0. Then, the

content of the least significant bit of the general register

rs

is set to the ISA mode bit (internal).

Since 32-bit length instructions must be word-aligned, a JR instruction must specify a target register (

rs

) that

contains an address whose two low-order bits are zero when a MIPS16 instruction can be executed. If these low-

order bits are not zero, an address error exception will occur when the jump target instruction is subsequently

fetched.

Operation:

32, 64 T:

temp ← GPR [rs]

T+1:

PC ← temp

63..1

|| 0

If MIPS16EN = 1 then

else

PC ← temp

endif

ISA MODE ← temp

0

Exceptions:

None