CHAPTER 2 V

R

4120A

76

Preliminary User’s Manual S15543EJ1V0UM

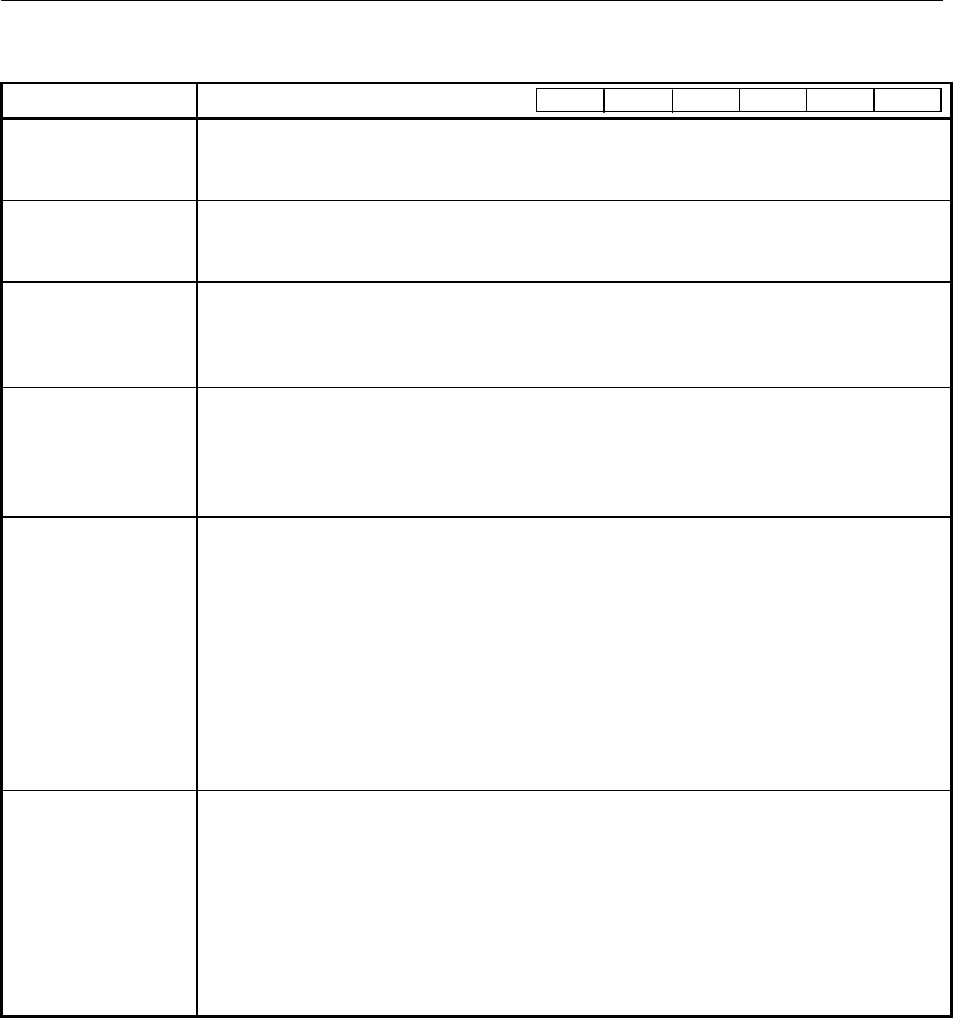

Table 2-13. Multiply/Divide Instructions (Extended ISA)

Instruction Format and Description

Doubleword Multiply DMULT rs, rt

The contents of registers rt and rs are multiplied, treating both operands as signed integers.

The 128-bit result is stored into special registers HI and LO.

Doubleword Multiply

Unsigned

DMULTU rs, rt

The contents of registers rt and rs are multiplied, treating both operands as unsigned integers.

The 128-bit result is stored into special registers HI and LO.

Doubleword Divide DDIV rs, rt

The contents of register rs are divided by that of register rt, treating both operands as signed integers.

The 64-bit quotient is stored into special register LO, and the 64-bit remainder is stored into special

register HI.

Doubleword Divide

Unsigned

DDIVU rs, rt

The contents of register rs are divided by that of register rt, treating both operands as unsigned

integers.

The 64-bit quotient is stored into special register LO, and the 64-bit remainder is stored into special

register HI.

Multiply and Add

Accumulate

MACC{h}{u}{s} rd, rs, rt

The contents of registers rt and rs are multiplied, treating both operands as 32-bit signed integers. The

result is added to the combined value of special registers HI and LO. The 64-bit result is stored into

special registers HI and LO.

If h=0, the same data as that stored in register LO is also stored in register rd; if h=1, the same data as

that stored in register HI is also stored in register rd.

If u is specified, the operand is treated as unsigned data.

If s is specified, registers rs and rd are treated as a 16-bit value (32 bits sign- or zero-extended), and

the value obtained by combining registers HI and LO is treated as a 32-bit value (64 bits sign- or zero-

extended). Moreover, saturation processing is performed for the operation result in the format

specified with u.

Doubleword Multiply

and Add Accumulate

DMACC{h}{u}{s} rd, rs, rt

The contents of registers rt and rs are multiplied, treating both operands as 32-bit signed integers. The

result is added to value of special register LO. The 64-bit result is stored into special register LO.

If h=0, the same data as that stored in register LO is also stored in register rd; if h=1, undefined data is

stored in register rd.

If u is specified, the operand is treated as unsigned data.

If s is specified, registers rs and rd are treated as a 16-bit value (32 bits sign- or zero-extended), and

register LO is treated as a 32-bit value (64 bits sign- or zero-extended). Moreover, saturation

processing is performed for the operation result in the format specified with u.

MFHI and MFLO instructions after a multiply or divide instruction generate interlocks to delay execution of the next

instruction, inhibiting the result from being read until the multiply or divide instruction completes.

Table 2-14 gives the number of processor cycles (PCycles) required to resolve interlock or stall between various

multiply or divide instructions and a subsequent MFHI or MFLO instruction.

op

rs rt

funct

r

d

sa