APPENDIX A MIPS III INSTRUCTION SET DETAILS

478

Preliminary User’s Manual S15543EJ1V0UM

DMACC

Doubleword Multiply and Accumulate (2/3)

DMACC

• When saturation processing is not executed (sat = 0): DMACC, DMACCU instructions

The contents of general register

rs

is multiplied by the contents of general register

rt

. If both operands are set

as "us = 1" (DMACCU instruction), the contents are handled as 32 bit unsigned data. If they are set as "us =

0" (DMACC instruction), the contents are handled as 32 bit signed integers. Sign/zero expansion by software

is required for any bits exceeding 32 bits in the operands.

The product of this multiply operation is added to the value in the LO special register. If us = 1, this add

operation handles the values being added as 64 bit unsigned data. If us = 0, the values are handled as 64 bit

signed integers.

The sum from this add operation is loaded to the LO special register. When hi = 1, data that is the same as

the data loaded to the HI special register is also loaded to the rd general register. When hi = 0, data that is

the same as the data loaded to the LO special register is also loaded to the rd general register. Overflow

exceptions do not occur.

These operations are defined for 64 bit mode and 32 bit kernel mode. A reserved instruction exception occurs if

one of these instructions is executed during 32 bit user/supervisor mode.

The correspondence of us and sat settings and values stored during saturation processing is shown below, along

with the hazard cycles required between execution of the instruction for manipulating the HI and LO registers and

execution of the DMACC instruction.

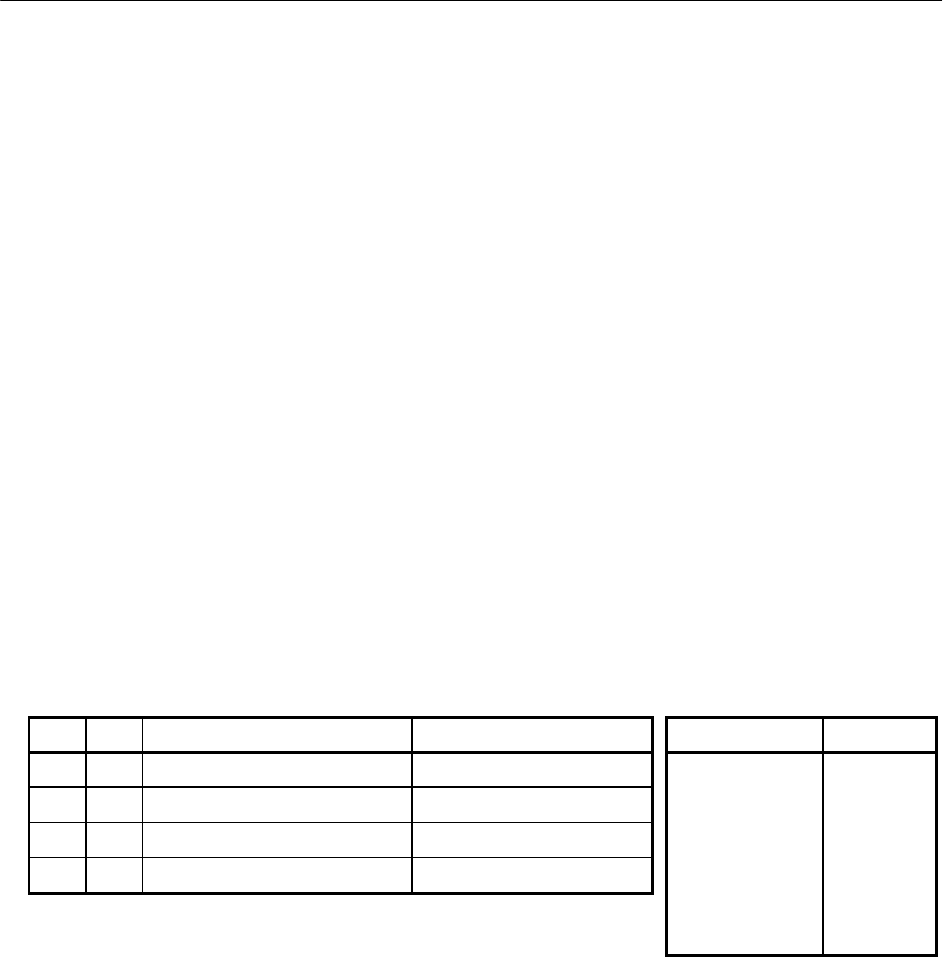

Values Stored during Saturation Processing Hazard Cycle Counts

us sat Overflow Underflow Instruction Cycle count

0 0 Store calculation result as is Store calculation result as is

1 0 Store calculation result as is Store calculation result as is

0 1 0000 0000 7FFF FFFFH FFFF FFFF 8000 0000H

1 1 FFFF FFFF FFFF FFFFH None

MULT, MULTU

DMULT, DMULTU

DIV, DIVU

DDIV, DDIVU

MFHI, MFLO

MTHI, MTLO

MACC

DMACC

1

3

36

68

2

0

0

0