CHAPTER 4 ATM CELL PROCESSOR

250

Preliminary User’s Manual S15543EJ1V0UM

4.5.1.2 Tx buffer directory

Tx buffer directory contains some buffer descriptors, up to 255, and a link pointer. Its address is word aligned. The

end of buffer directory must be a link pointer. Buffer descriptors must be read and served from the top in a sequential

manner.

4.5.1.3 Tx buffer descriptor

Both a Tx buffer descriptor and a Tx link pointer consist of 2 words. DL bit, bit 30 of the first word, indicates that

these two words are a buffer descriptor (DL = 1) or a link pointer (DL = 0). In the Tx buffer descriptor, L bit, bit 31,

indicates that the buffer pointed by this descriptor contains the last portion of a packet.

A Tx link pointer is shown as Figure 4-11. L bit, bit 31, is fixed to zero. If there is no buffer directory to be linked,

directory address of link pointer must be zero, as a null pointer.

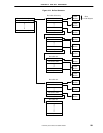

Figure 4-11. Tx Buffer Descriptor/Link Pointer

Tx buffer directory Address

-Tx link pointer

Attribute

-Tx buffer descriptor

31 30 016 15

Attribute SizeL

0

Buffer Address

31 0

DL

31 30

0

DL

4.5.1.4 Data buffer

Data buffer contains actual packet data to be sent. Size of a buffer can vary from 1 byte to 64 Kbytes. Its address is

byte aligned.

4.5.2 Rx pool structure

Rx buffer structure is defined as a pool. Eight pools are supported. A pool is composed of chain of Rx buffer

directories. Each Rx buffer directory has some buffer descriptors and a link pointer. Each buffer descriptor points a

buffer string of received cell data. A link pointer has an address to a next Rx buffer directory.

VR

4120A will create up to 8 pools and give them to ATM Cell Processor.