CHAPTER 2 V

R

4120A

Preliminary User’s Manual S15543EJ1V0UM

61

2.1.4 Data formats and addressing

The V

R

4120A uses following four data formats:

✧ Doubleword (64 bits)

✧ Word (32 bits)

✧ Halfword (16 bits)

✧ Byte (8 bits)

For the

µ

PD98502, byte ordering within all of the larger data formats - halfword, word, doubleword - can be

configured in either big-endian or little-endian order.

Endianness refers to the location of byte 0 within the multi-byte data structure.

When configured as a little-endian system, byte 0 is always the least-significant (rightmost) byte, which is

compatible with iAPX™ and DEC VAX™ conventions. Figures 2-4 and 2-5 show this configuration.

Figure 2-4. Little-Endian Byte Ordering in Word Data

12

12131415

01516 82324 731

8

891011

4

4567

0

0123

Low-order

address

High-order

address

Word

address

Bit No.

Remarks 1. The lowest byte is the lowest address.

2. The address of word data is specified by the lowest byte’s address.

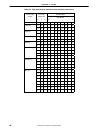

Figure 2-5. Little-Endian Byte Ordering in Double Word Data

16

23

03132

87

63

8

0

Low-order

address

High-order

address

Double word

address

Half word

22

15 14

7 6

21 20

13 12

5 4

19 18

11 10

3 2

17 16

9 8

1 0

16 15

Word

Byte

48 47

Remarks 1. The lowest byte is the lowest address.

2. The address of word data is specified by the lowest byte’s address.

The CPU core uses the following byte boundaries for halfword, word, and doubleword accesses:

Halfword: An even byte boundary (0, 2, 4...)

Word: A byte boundary divisible by four (0, 4, 8...)

Doubleword: A byte boundary divisible by eight (0, 8, 16...)