CHAPTER 2 V

R

4120A

Preliminary User’s Manual S15543EJ1V0UM

59

2.1.2 VR4120A registers

The V

R

4120A has the following registers.

general-purpose register (GPR): 64 bits × 32

In addition, the processor provides the following special registers:

64-bit Program Counter (PC)

64-bit HI register, containing the integer multiply and divide upper doubleword result

64-bit LO register, containing the integer multiply and divide lower doubleword result

Two of the general-purpose registers have assigned the following functions:

r0 is hardwired to a value of zero, and can be used as the target register for any instruction whose result is to

be discarded. r0 can also be used as a source when a zero value is needed.

r31 is the link register used by link instruction, such as JAL (Jump and Link) instructions. This register can be

used for other instructions. However, be careful that use of the register by a link instruction will not coincide

with use of the register for other operations.

The register group is provided within the CP0 (system control coprocessor), to process exceptions and to manage

addresses.

CPU registers can operate as either 32-bit or 64-bit registers, depending on the V

R

4120A processor operation

mode.

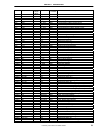

Figure 2-2 shows the CPU registers.

Figure 2-2. VR4120A Registers

General-purpose register

r0 = 0

031

Multiply/divide register3263

HI

0313263

LO

Program Counter

0

PC

0

63

63

r1

r2

⋅

⋅

⋅

⋅

r29

r30

r31 = LinkAddress

3132

3132

The V

R

4120A has no Program Status Word (PSW) register as such; this is covered by the Status and Cause

registers incorporated within the System Control Coprocessor (CP0).

The CP0 registers are used for exception handling or address management. The overview of these registers is

described in 2.1.5 Coprocessors (CP0).