AMD Geode™ LX Processors Data Book 155

CPU Core Register Descriptions

33234H

5.5.2.58 L1 Instruction TLB Index (ITB_INDEX_MSR)

The L1 Instruction TLB is accessible via an index/data mechanism. The index of the entry to access is set via

ITB_INDEX_MSR and an entry is read or written via ITB_ENTRY_MSR or ITB_ENTRY_I_MSR. An autoincrement mecha-

nism is provided to post-increment ITB_INDEX_MSR after every access to ITB_ENTRY_I_MSR. The L0 TLB can be

accessed by a read only MSR and it is not necessary to use the ITB_INDEX_MSR to read the L0 TLB. The L1 TLB LRU

bits can be accessed using the ITB_LRU_MSR. Diagnostic accesses to the L0 or L1 Instruction TLB array do not affect the

values of the LRU bits.

Note that the L1 Instruction TLB is always in use and cannot be disabled. That means that diagnostic accesses generated

by code running on the processor are unreliable at best, since the TLB contents may be changing while the code is running.

Furthermore, the L1 Instruction TLB is flushed on any mode change, so a debug handler would no longer see the TLB con-

tents prior to the DMI. Thus the L1 Instruction TLB accesses are intended only to be used by the GLCP after the pipeline

has been halted.

L0_IC_TAG_I_MSR Bit Descriptions

Bits Name Description

63:32 RSVD Reserved.

31:16 TLB_NUM TLB Number. This is the one-hot-value of the TLB entry corresponding to the L0 cache

entry. (Default = 0)

15:12 RSVD Reserved.

11:8 TAG Tag/Line. This is a combination of the 4-bit tag and the 5-bit line. Together they make up

bits [11:3] of the physical address for the line selected by IC_INDEX_MSR (MSR

00001710h).

7:3 LINE

2:1 RSVD Reserved.

0V Valid. Valid bit for the line selected by IC_INDEX_MSR (MSR 00001710h). (Default = 0)

MSR Address 00001720h

Typ e R /W

Reset Value 00000000_0000000xh

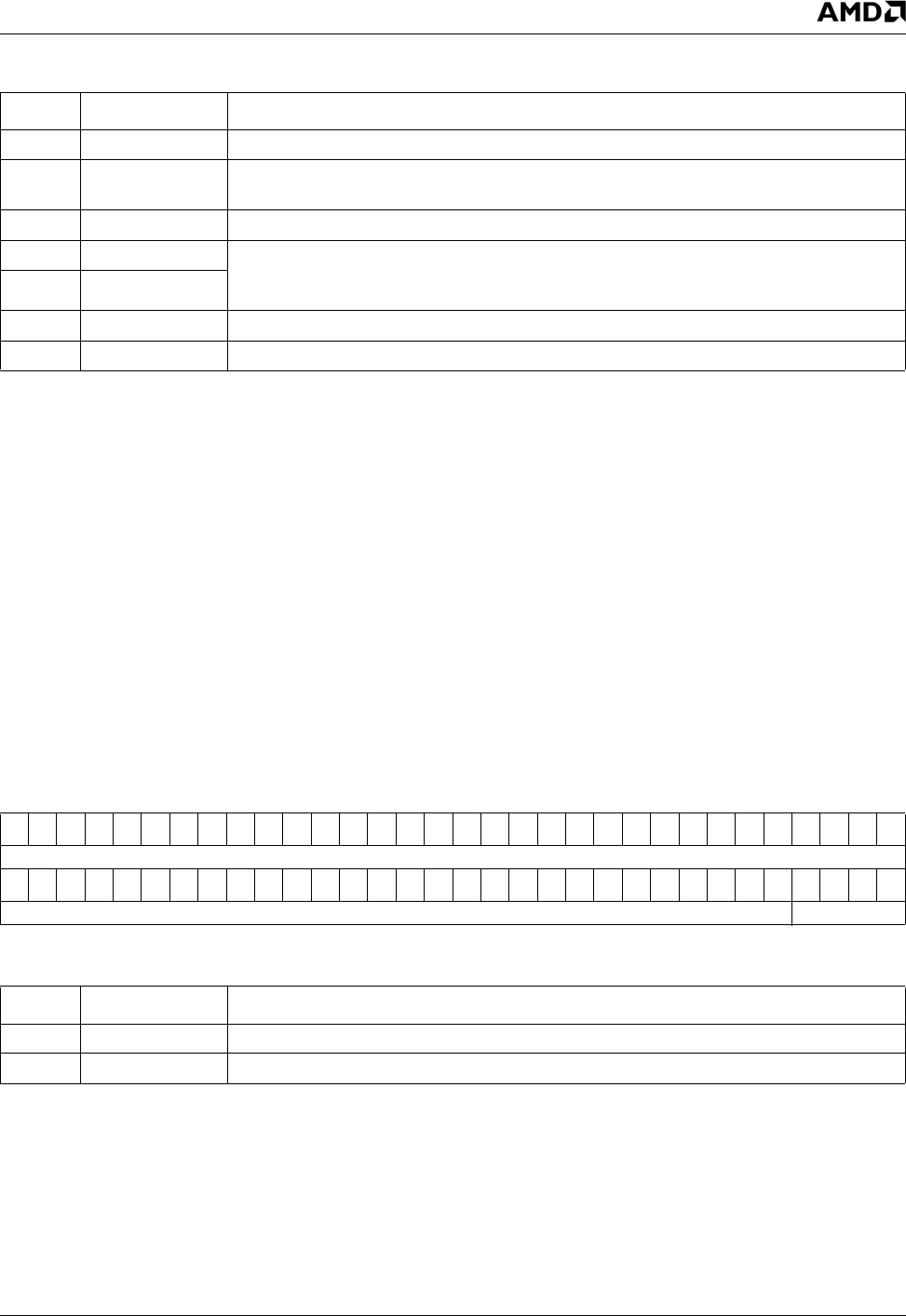

ITB_INDEX_MSR Register Map

63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32

RSVD

313029282726252423222120191817161514131211109876543210

RSVD INDEX

ITB_INDEX_MSR Bit Descriptions

Bits Name Description

63:4 RSVD Reserved.

3:0 INDEX Index.