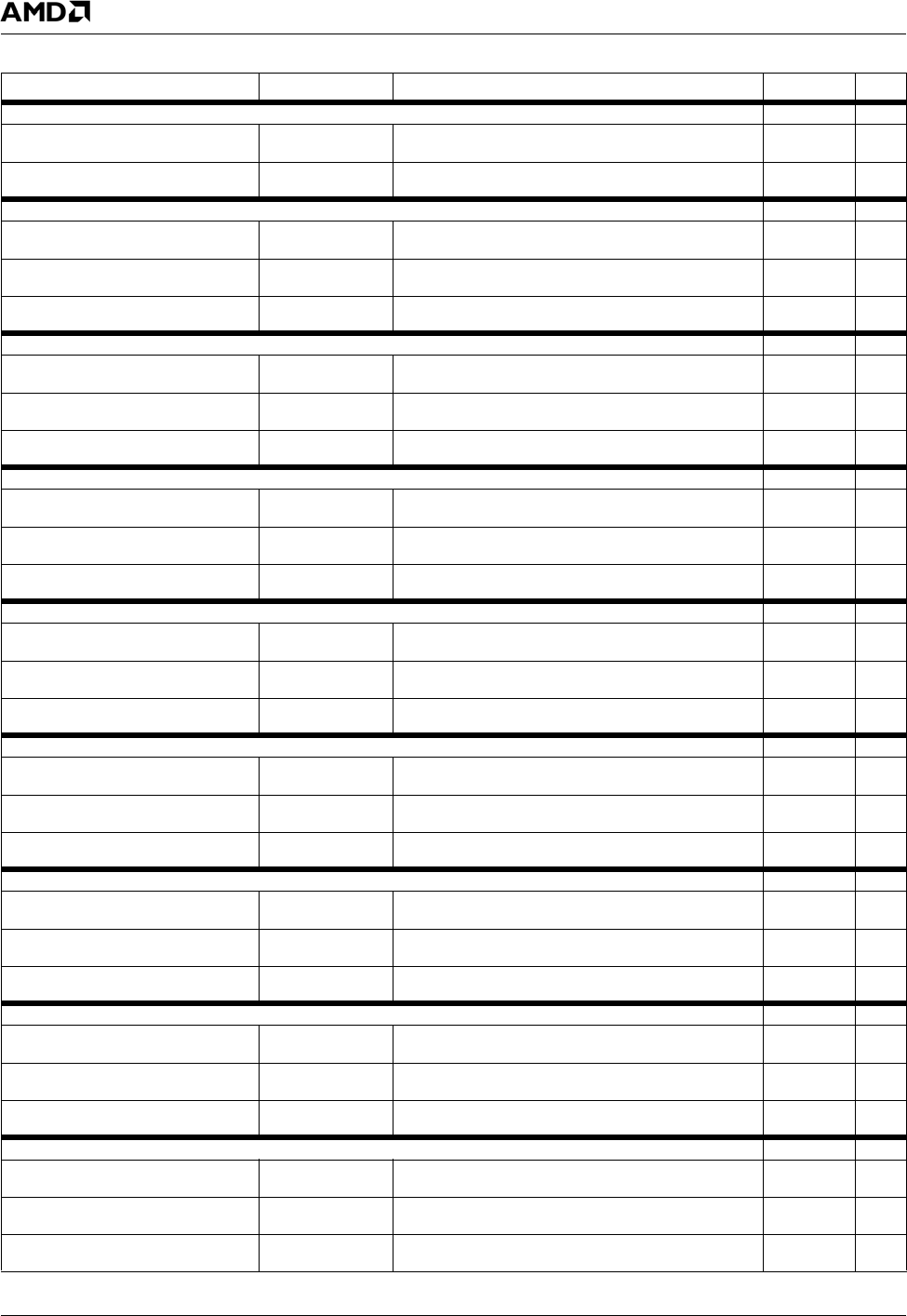

664 AMD Geode™ LX Processors Data Book

Instruction Set

33234H

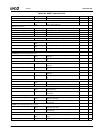

PSHUFW Packed Shuffle Word

MMX Register1, MMX Register2,

imm8

0F70 [11 mm1 mm2]

#

MMX reg 1 [word] <--- MMX reg 2 [windexall (imm8)] 2

MMX Register, Memory64, imm8 0F70 [mod mm r/m]

#

MMX reg [word] <--- Memory64 [windexall (imm8)] 2

PSLLD Packed Shift Left Logical Dword

MMX Register 1 by MMX Register 2 0FF2 [11 mm1

mm2]

MMX reg 1 [dword] <--- MMX reg 1 [dword] shift left by MMX

reg 2 [dword], shifting in zeroes

2

MMX Register by Memory 0FF2 [mod mm r/m] MMX reg [dword] <--- MMX reg [dword] shift left by

memory [dword], shifting in zeroes

2

MMX Register by immediate 0F72 [11 110 mm] # MMX reg [dword] <--- MMX reg [dword] shift left by [im byte],

shifting in zeroes

2

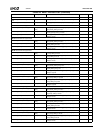

PSLLQ Packed Shift Left Logical Qword

MMX Register 1 by MMX Register 2 0FF3 [11 mm1

mm2]

MMX reg 1 [qword] <--- MMX reg 1 [qword] shift left by MMX

reg 2 [qword], shifting in zeroes

2

MMX Register by Memory 0FF3 [mod mm r/m] MMX reg [qword] <--- MMX reg [qword] shift left by memory

[qword], shifting in zeroes

2

MMX Register by immediate 0F73 [11 110 mm] # MMX reg [qword] <--- MMX reg [qword]shift left by [im byte],

shifting in zeroes

2

PSLLW Packed Shift Left Logical Word

MMX Register 1 by MMX Register 2 0FF1 [11 mm1

mm2]

MMX reg 1 [word] <--- MMX reg 1 [word] shift left by MMX reg

2 [word], shifting in zeroes

2

MMX Register by Memory 0FF1 [mod mm r/m] MMX reg [word] <--- MMX reg [word] shift left by memory

[word], shifting in zeroes

2

MMX Register by immediate 0F71 [11 110mm] # MMX reg [word] <--- MMX reg [word] shift left by [im byte],

shifting in zeroes

2

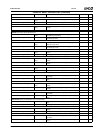

PSRAD Packed Shift Right Arithmetic Dword

MMX Register 1 by MMX Register 2 0FE2 [11 mm1

mm2]

MMX reg 1 [dword] <--- MMX reg 1 [dword] shift right by MMX

reg 2 [dword], shifting in sign bits

2

MMX Register by Memory 0FE2 [mod mm r/m] MMX reg [dword] <--- MMX reg [dword] shift right by memory

[dword], shifting in sign bits

2

MMX Register by immediate 0F72 [11 100 mm] # MMX reg [dword] <--- MMX reg [dword] shift right by [im byte],

shifting in sign bits

2

PSRAW Packed Shift Right Arithmetic Word

MMX Register 1 by MMX Register 2 0FE1 [11 mm1

mm2]

MMX reg 1 [word] <--- MMX reg 1 [word] shift right by MMX

reg 2 [word], shifting in sign bits

2

MMX Register by Memory 0FE1 [mod mm r/m] MMX reg [word] <--- MMX reg [word] shift right by memory

[word], shifting in sign bits

2

MMX Register by immediate 0F71 [11 100 mm] # MMX reg [word] <--- MMX reg [word] shift right by [im byte],

shifting in sign bits

2

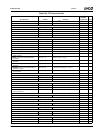

PSRLD Packed Shift Right Logical Dword

MMX Register 1 by MMX Register 2 0FD2 [11 mm1

mm2]

MMX reg 1 [dword] <--- MMX reg 1 [dword] shift right by MMX

reg 2 [dword], shifting in zeroes

2

MMX Register by Memory 0FD2 [mod mm r/m] MMX reg [dword] <--- MMX reg [dword] shift right by mem-

ory[dword], shifting in zeroes

2

MMX Register by immediate 0F72 [11 010 mm] # MMX reg [dword] <--- MMX reg [dword]shift right by [im byte],

shifting in zeroes

2

PSRLQ Packed Shift Right Logical Qword

MMX Register 1 by MMX Register 2 0FD3 [11 mm1

mm2]

MMX reg 1 [qword] <--- MMX reg 1 [qword] shift right by MMX

reg 2 [qword], shifting in zeroes

3

MMX Register by Memory 0FD3 [mod mm r/m] MMX reg [qword] <--- MMX reg [qword] shift right by memory

[qword], shifting in zeroes

3

MMX Register by immediate 0F73 [11 010 mm] # MMX reg [qword] <--- MMX reg [qword] shift right by [im byte],

shifting in zeroes

3

PSRLW Packed Shift Right Logical Word

MMX Register 1 by MMX Register 2 0FD1 [11 mm1

mm2]

MMX reg 1 [word] <--- MMX reg 1 [word] shift right by MMX

reg 2 [word], shifting in zeroes

2

MMX Register by Memory 0FD1 [mod mm r/m] MMX reg [word] <--- MMX reg [word] shift right by memory

[word], shifting in zeroes

2

MMX Register by immediate 0F71 [11 010 mm] # MMX reg [word] <--- MMX reg [word] shift right by imm [word],

shifting in zeroes

2

Table 8-28. MMX™ Instruction Set (Continued)

MMX™ Instructions Opcode Operation Clock Ct Notes