658 AMD Geode™ LX Processors Data Book

Instruction Set

33234H

8.4 MMX™, FPU, and AMD 3DNow!™ Technology Instructions Sets

The CPU is functionally divided into the Floating Point Unit (FPU) unit and the Integer Unit. The FPU has been extended to

process MMX, AMD 3DNow!, and floating point instructions in parallel with the Integer Unit.

When the Integer Unit detects an MMX instruction, the instruction is passed to the FPU or execution. The Integer Unit con-

tinues to execute instructions while the FPU executes the MMX instruction. If another MMX instruction is encountered, the

second MMX instruction is placed in the MMX queue. Up to six MMX instructions can be queued.

When the Integer Unit detects a floating point instruction without memory operands, after two clock cycles the instruction

passes to the FPU for execution. The Integer Unit continues to execute instructions while the FPU executes the floating

point instruction. If another FPU instruction is encountered, the second FPU instruction is placed in the FPU queue. Up to

four FPU instructions can be queued. In the event of an FPU exception, while other FPU instructions are queued, the state

of the CPU is saved to ensure recovery.

The MMX instruction set (including extensions) is summarized in Table 8-28. The FPU instruction set is summarized in

Table 8-29. The AMD 3DNow! instruction set (including extensions) is summarized in Table 8-30. The abbreviations used in

the instruction sets are listed in Table 8-27.

Note: The following opcodes are reserved: D9D7, D9E2, D9E7, DDFC, DED8, DEDA, DEDC, DEDD, DEDE, and DFFC.

If a reserved opcode is executed, unpredictable results may occur (exceptions are not generated).

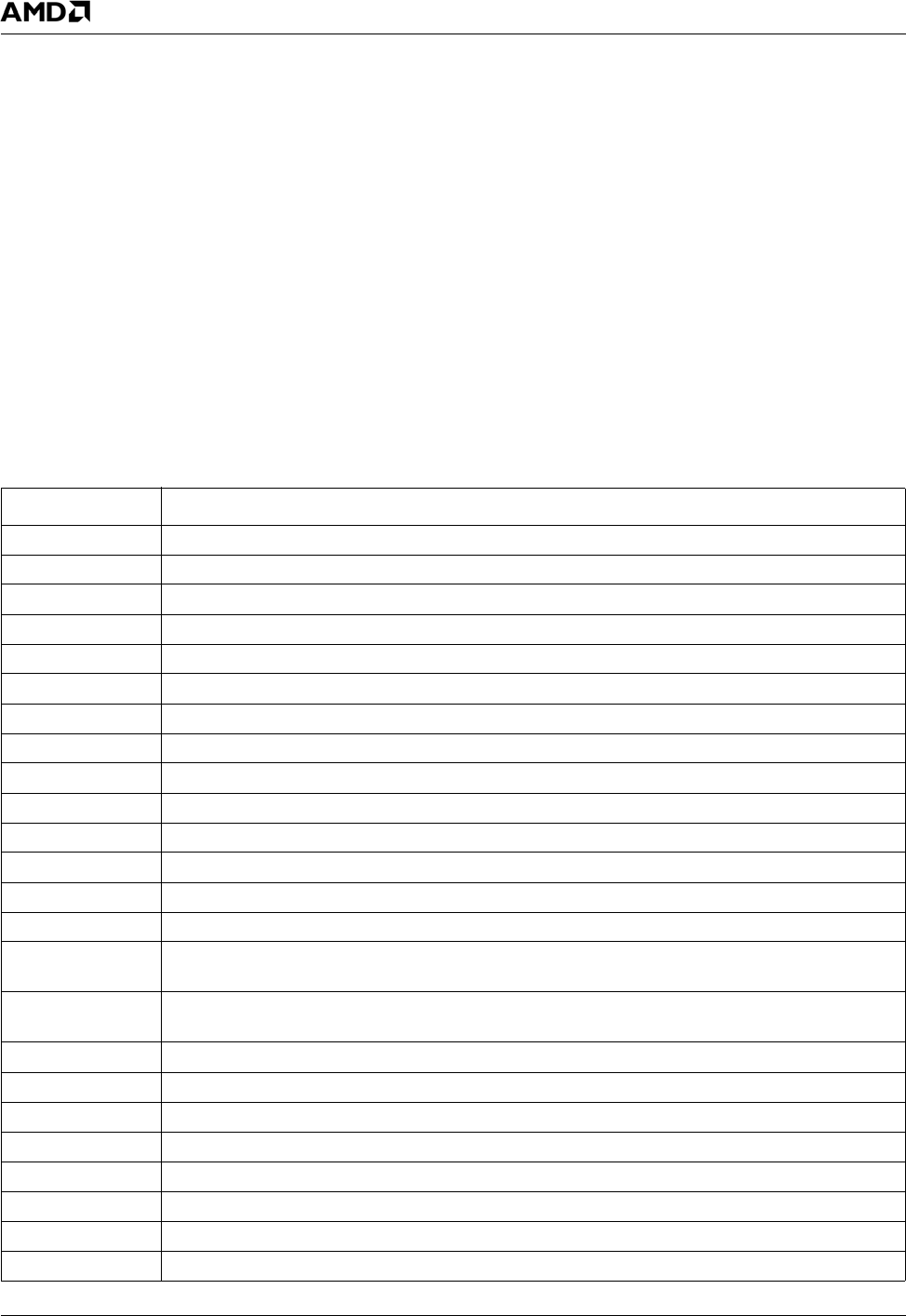

Table 8-27. MMX™, FPU, and AMD 3DNow!™ Instruction Set Table Legend

Abbreviation Description

<--- Result written.

[11 mm reg] Binary or binary groups of digits.

mm One of eight 64-bit MMX registers.

reg A general purpose register.

<--- sat --- If required, the resultant data is saturated to remain in the associated data range.

<--- move --- Source data is moved to result location.

[byte] Eight 8-bit BYTEs are processed in parallel.

[word] Four 16-bit WORDs are processed in parallel.

[dword] Two 32-bit DWORDs are processed in parallel.

[qword] One 64-bit QWORD is processed.

[sign xxx] The BYTE, WORD, DWORD, or QWORD most significant bit is a sign bit.

mm1, mm2 MMX Register 1, MMX Register 2.

mod r/m Mod and r/m byte encoding (Table 8-8 on page 622).

pack Source data is truncated or saturated to next smaller data size, then concatenated.

packdw Pack two DWORDs from source and two DWORDs from destination into four WORDs in the Desti-

nation register.

packwb Pack four WORDs from source and four WORDs from destination into eight BYTEs in the Destina-

tion register.

imm8 One-byte of immediate value.

memory64 64 bits in memory located in eight consecutive bytes.

memory32 32 bits in memory located in four consecutive bytes.

index 0 (imm8) The value imm8 [1:0] *16.

index 1 (imm8) The value imm8 [3:2] *16.

index 2 (imm8) The value imm8 [5:4] *16.

index 3 (imm8) The value imm8 [7:6] *16.

windex 0 (imm8) The range given by [index0 (imm8) + 15: index0 (imm8)].