AMD Geode™ LX Processors Data Book 663

Instruction Set

33234H

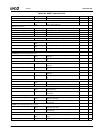

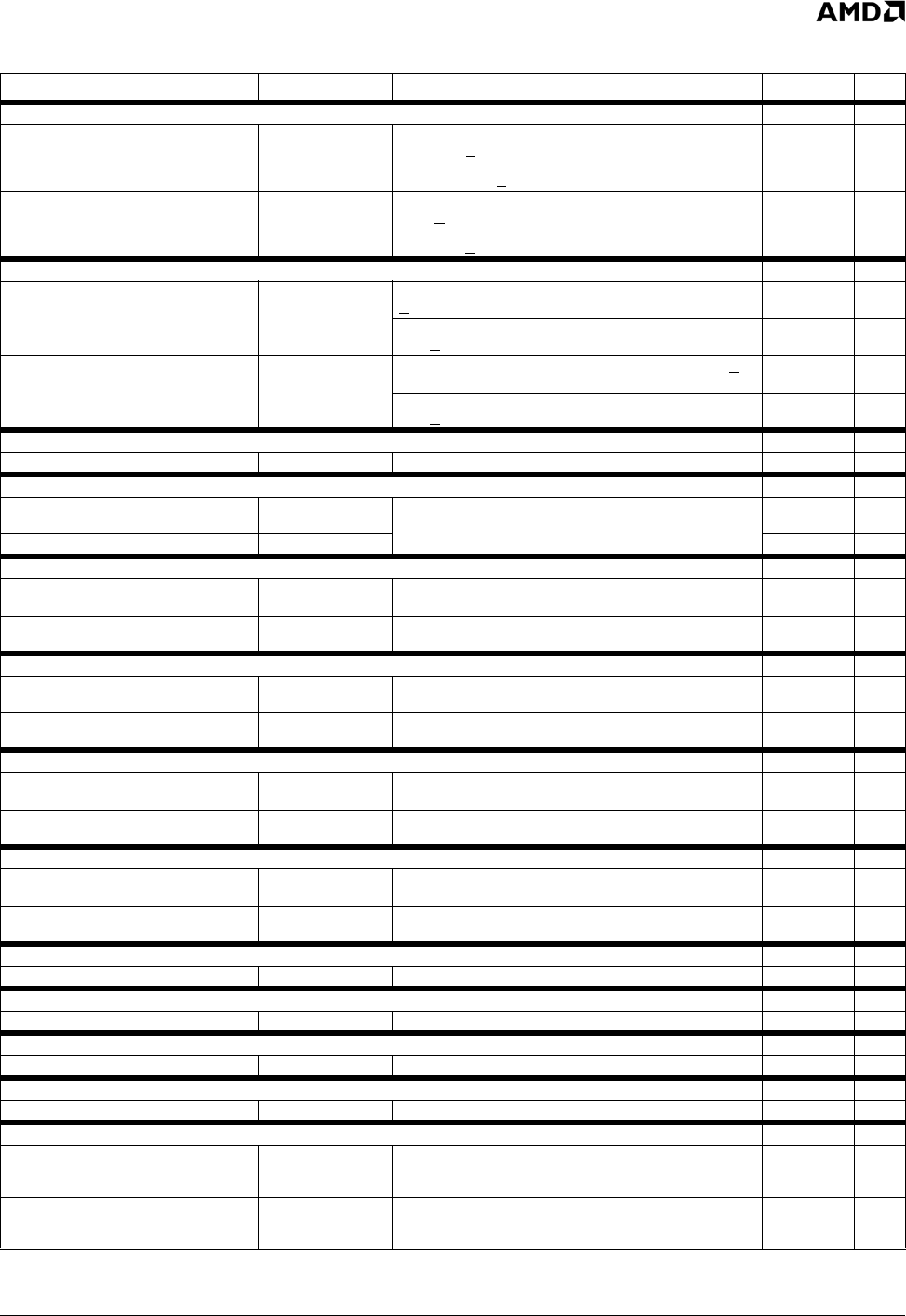

PMINSW Packed Minimum Signed Word

MMX Register 1with MMX Register 2 0FEA [11 mm1

mm2]

MMX reg 1 [word] <--- MMX reg 1 [word] --- if (MMX reg 1

[sign word]

< MMX reg 2 [sign word])

MMX reg 1 [word] <--- MMX reg 2 [word] --- if (MMX reg 1

[sign word] NOT

< MMX reg 2 [sign word])

2

MMX Register 1with Memory64 0FEA [mod mm r/m] MMX reg [word] <--- MMX reg 1 [word] --- if (MMX reg [sign

word]

< Memory64 [sign word])

MMX reg [word] <--- Memory64 [word] --- if (MMX reg [sign

word] NOT

< Memory64 [sign word])

2

PMINUB Packed Minimum Unsigned Byte

MMX Register 1with MMX Register 2 0FDA [11 mm1

mm2]

MMX reg 1 [byte] <--- MMX reg 1 [byte] --- if (MMX reg 1 [byte]

< MMX reg 2 [byte])

2

MMX reg 1 [byte] <--- MMX reg 2 [byte] --- if (MMX reg 1 [byte]

NOT

< MMX reg 2 [byte])

2

MMX Register 1with Memory64 0FDA [mod mm r/m] MMX reg [byte] <--- MMX reg [byte] --- if (MMX reg [byte]

<

Memory64 [byte])

2

MMX reg [byte] <--- Memory64 [byte] --- if (MMX reg [byte]

NOT

< Memory64 [byte])

2

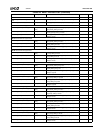

PMOVMSKB Move Byte Mask to Integer Register 1

Register 32 with MMX Register 0FD7 [11 reg mm] reg32 <--- zero extend, MSB [bytes]

PMULHRW Packed Multiply High with Rounding

MMX Register 2 to MMX Register 1 0FB7 [11 mm1

mm2]

Multiply the signed packed word in the MMX register/memory

with the signed packed word in the MMX register. Round with

1/2 bit 15, and store bits 30 - 15 of result in the MMX register.

2

Memory to MMX Register 0FB7 [mod mm r/m] 2

PMULHUW Packed Multiply High Unsigned Word

MMX Register1 with MMX Register2 0FE4 [11 mm1

mm2]

MMX reg 1 [word] <--- high word --- (MMXreg 1[word] * MMX

reg 2 [word])

2

MMX Register with Memory64 0FE4 [mod mm r/m] MMX reg [word] <--- high word --- (MMX reg [word] *

Memory64 [word])

2

PMULHW Packed Multiply High

MMX Register 2 to MMX Register 1 0FE5 [11 mm1

mm2]

MMX reg 1 [word] <--- high word --- (MMX reg 1 [sign word] *

MMX reg 2 [sign word])

2

Memory to MMX Register 0FE5 [mod mm r/m] MMX reg [word] <--- high word --- MMX reg [sign word] *

Memory64 [sign word]

2

PMULLW Packed Multiply Low

MMX Register 2 to MMX Register 1 0FD5 [11 mm1

mm2]

MMX reg 1 [word] <--- low word --- (MMX reg 1 [sign word] *

MMX reg 2 [sign word])

2

Memory to MMX Register 0FD5 [mod mm r/m] MMX reg 1 [word] <--- low word --- (MMX reg [sign word] *

Memory64 [sign word])

2

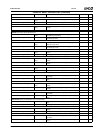

POR Bitwise OR

MMX Register 2 to MMX Register 1 0FEB [11 mm1

mm2]

MMX reg 1 [qword] <--- MMX reg 1 [qword] logic OR MMX reg

2 [qword]

2

Memory to MMX Register 0FEB [mod mm r/m] MMX reg [qword] <--- MMX reg [qword] logic OR memory64

[qword]

2

PREFETCH NTA Move Data Closer to the Processor using the NTA Register

Memory8 0F18 [mod 000 r/m]

PREFETCH0 Move Data Closer to the Processor using the T0 Register

Memory8 0F18 [mod 001 r/m]

PREFETCH1 Move Data Closer to the Processor using the T1 Register

Memory8 0F18 [mod 010 r/m]

PREFETCH2 Move Data Closer to the Processor using the T2 Register

Memory8 0F18 [mod 011 r/m]

PSADBW Packed Sum of Absolute Byte Differences

MMX Register1 with MMX Register2 0FF6 [11 mm1

mm2]

MMX reg 1 [low word] <--- Sum --- (abs --- (MMXreg 1[byte] -

MMX reg 2 [byte]))

MMX reg 1 [upper three words] <--- 0

3

MMX Register with Memory64 0FF6 [mod mm r/m] MMX reg [low word] <--- Sum --- (abs --- (MMX reg [byte] -

Memory64 [byte]))

MMX reg [up three word] <--- 0

3

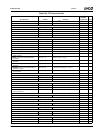

Table 8-28. MMX™ Instruction Set (Continued)

MMX™ Instructions Opcode Operation Clock Ct Notes