AMD Geode™ LX Processors Data Book 575

GeodeLink™ PCI Bridge Register Descriptions

33234H

6.16.1.3 GLD SMI MSR (GLD_MSR_SMI)

MSR Address 50002002h

Typ e R /W

Reset Value 00000000_0000003Fh

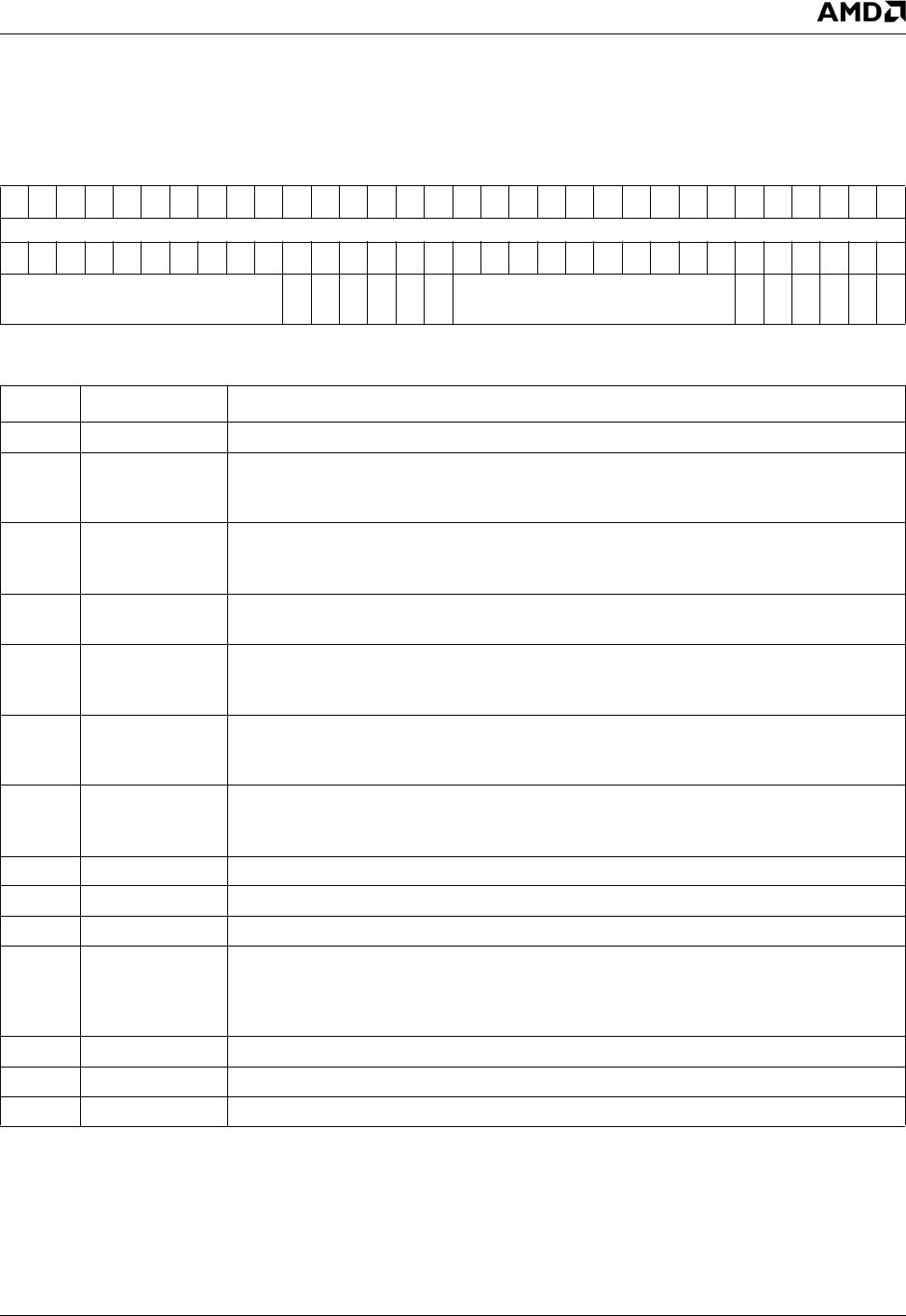

GLD_MSR_SMI Register Map

63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32

RSVD

313029282726252423222120191817161514131211109876543210

RSVD

PARE

SYSE

VPHE

BME

TARE

MARE

RSVD

PARM

SYSM

VPHM

BMM

TARM

MARM

GLD_MSR_SMI Bit Descriptions

Bit Name Description

63:22 RSVD (RO) Reserved (Read Only). Reserved for future use.

21 PARE Parity Error Event (Read/Write-1-to-Clear). This bit is asserted due to detection of a

PCI bus parity error. Write 1 to clear. PS (MSR 50002010h[27]) must be set to enable this

event. The event causes an ASMI if PARM (bit 5) is cleared.

20 SYSE System Error Event (Read/Write-1-to-Clear). This bit is asserted due to the detection

of a PCI bus system error. Write 1 to clear. PS (MSR 50002010h[27]) must be set to

enable this event. The event causes an ASMI if SYSM (bit 4) is cleared.

19 VPHE Virtual PCI Header Event (Read/Write-1-to-Clear). This bit is set by Virtual PCI Header

support logic, write 1 to clear. The event causes an SSMI if VPHM (bit 3) is cleared.

18 BME Broken Master Event (Read/Write-1-to-Clear). This bit is asserted due to detection of a

broken PCI bus master. Write 1 to clear. BMS (MSR 50002010h[26]) must be set to

enable this event. The event causes an ASMI if BMM (bit 2) is cleared.

17 TARE Target Abort Received Event (Read/Write-1-to-Clear). This bit is asserted due to

reception of target abort on PCI. Write 1 to clear. TARS (MSR50002010h[25]) must be

set to enable this event. The event causes an ASMI if TARM (bit 1) is cleared.

16 MARE Master Abort Received Event (Read/Write-1-to-Clear). This bit is asserted due to

reception of master abort on PCI. Write 1 to clear. MARS (MSR 50002010h[24]) must be

set to enable this event. The event causes an ASMI if MARM (bit 0) is cleared.

15:6 RSVD Reserved. Reserved for future use.

5PARM Parity Error Mask. Clear to allow PARE (bit 21) to generate an ASMI.

4 SYSM System Error Mask. Clear to allow SYSE (bit 20) to generate an ASMI.

3 VPHM Virtual PCI Header Mask. Clear to allow SSMI flag to be set in selected GLIU response

packets. I/O reads and writes to location 0CFCh may cause an SSMI depending upon

the configuration of this bit and the GLPCI_PBUS (MSR 50002012h) model specific reg-

isters.

2BMM Broken Master Mask. Clear to allow BME (bit 18) to generate an ASMI.

1TARM Target Abort Received Mask. Clear to allow TARE (bit 17) to generate an ASMI.

0MARM Master Abort Received Mask. Clear to allow MARE (bit 16) to generate an ASMI.