472 AMD Geode™ LX Processors Data Book

Video Input Port

33234H

.

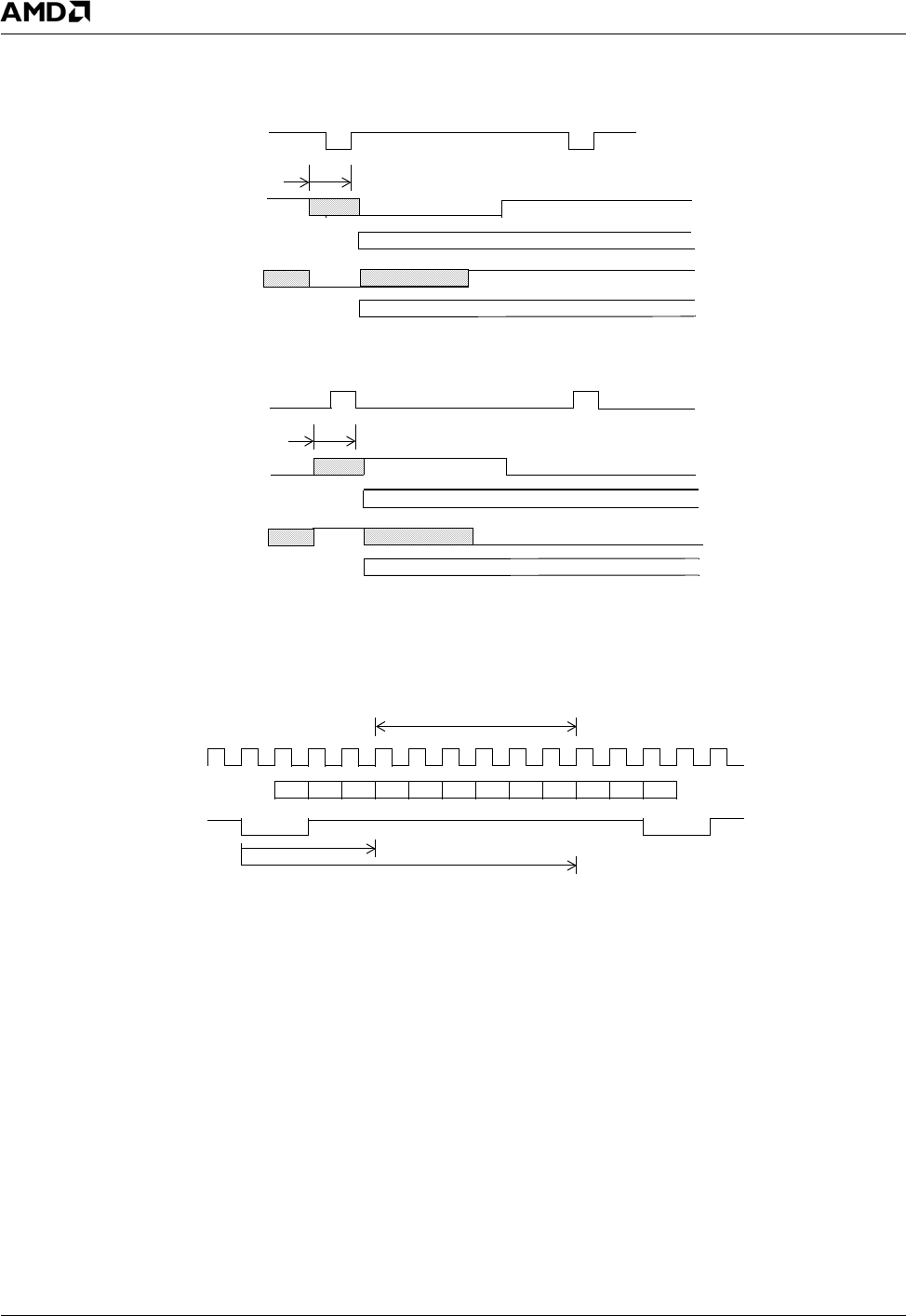

Figure 6-46. BT.601 Mode Programmable Field Detection

Figure 6-47. BT.601 Mode Horizontal Timing

HSYNC

VSYNC

odd_field_detect_start

field_detect_duration

ACTIVE LOW HSYNC/VSYNC (HSYNC Polarity = 0 / VSYNC Polarity = 0)

ACTIVE HIGH HSYNC/VSYNC (HSYNC Polarity = 1 / VSYNC Polarity = 1)

VSYNC

(for odd field)

(for even field)

even field

odd field

line #1

HSYNC

VSYNC

odd_field_detect_start

field_detect_duration

VSYNC

(for odd field)

(for even field)

even field

odd field

line #1

A = 3

B = 12

A - horizontal_start for 601 (VIP Memory Offset 3Ch)

CLK

HSYNC

B - horizontal_end for 601 (VIP Memory Offset 38h)

video data

* Clock #1 occurs at leading transition of HSYNC

2

1*

3

D2 D3 D4 D5 D6

4

D1

10

115

6

7

8

9