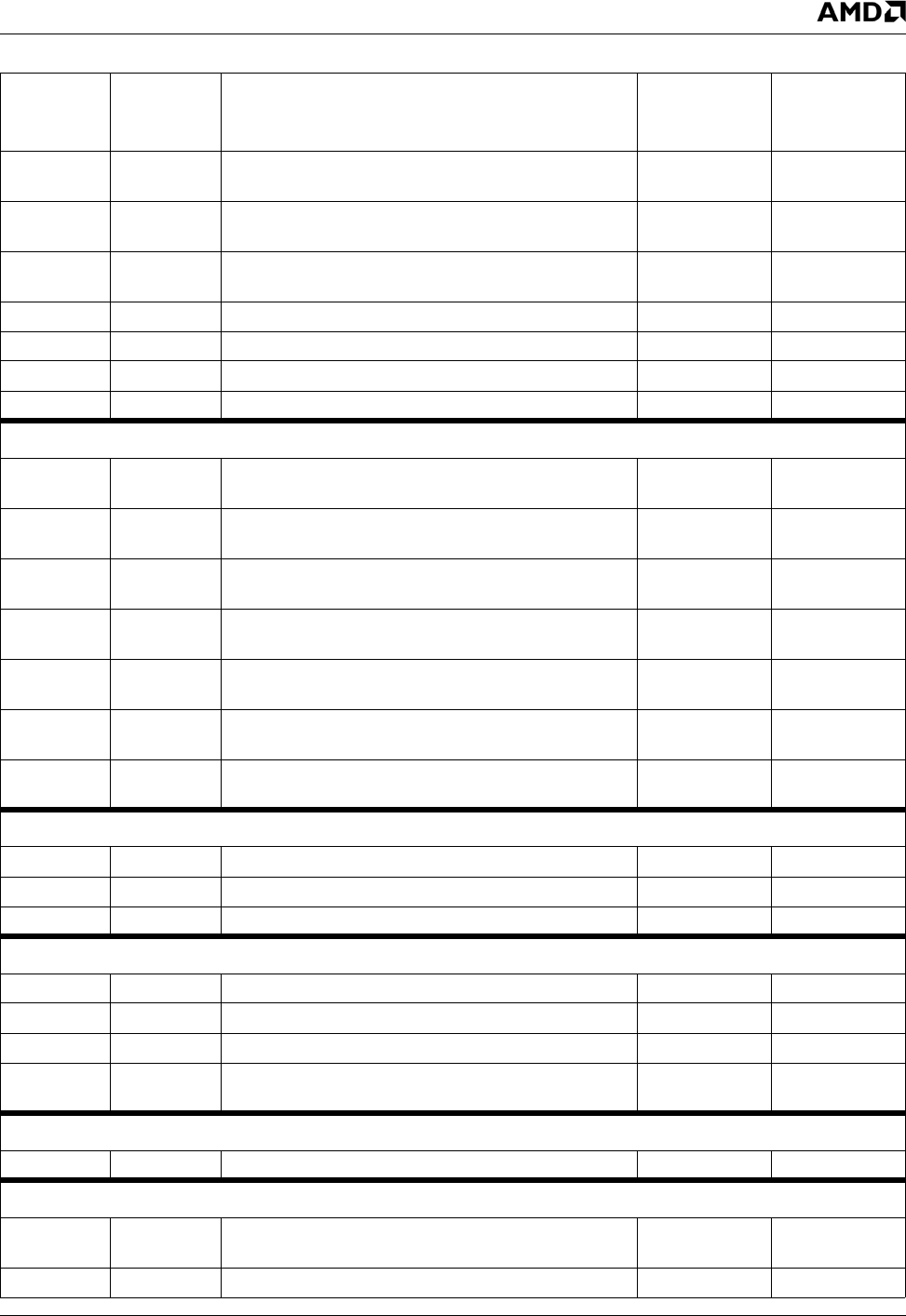

AMD Geode™ LX Processors Data Book 301

Display Controller Register Descriptions

33234H

020h R/W DC Video Y Buffer Start Address Offset

(DC_VID_Y_ST_OFFSET)

xxxxxxxxh Page 323

024h R/W DC Video U Buffer Start Address Offset

(DC_VID_U_ST_OFFSET)

xxxxxxxxh Page 323

028h R/W DC Video V Buffer Start Address Offset

(DC_VID_V_ST_OFFSET)

xxxxxxxxh Page 324

02Ch R/W DC Dirty/Valid Region Top (DC_DV_TOP) 00000000h Page 324

030h R/W DC Line Size (DC_LINE_SIZE) xxxxxxxxh Page 325

034h R/W DC Graphics Pitch (DC_GFX_PITCH) xxxxxxxxh Page 326

038h R/W DC Video YUV Pitch (DC_VID_YUV_PITCH) xxxxxxxxh Page 326

Timing Registers

040h R/W DC Horizontal and Total Timing

(DC_H_ACTIVE_TIMING)

xxxxxxxxh Page 328

044h R/W DC CRT Horizontal Blanking Timing

(DC_H_BLANK_TIMING)

xxxxxxxxh Page 329

048h R/W DC CRT Horizontal Sync Timing

(DC_H_SYNC_TIMING)

xxxxxxxxh Page 329

050h R/W DC Vertical and Total Timing

(DC_V_ACTIVE_TIMING)

xxxxxxxxh Page 330

054h R/W DC CRT Vertical Blank Timing

(DC_V_BLANK_TIMING)

xxxxxxxxh Page 331

058h R/W DC CRT Vertical Sync Timing

(DC_V_SYNC_TIMING)

xxxxxxxxh Page 331

05Ch R/W DC Frame Buffer Active Region Register

(DC_FB_ACTIVE)

xxxxxxxxh Page 332

Cursor Position and Count Status Registers

060h R/W DC Cursor X Position (DC_CURSOR_X) xxxxxxxxh Page 332

064h R/W DC Cursor Y Position (DC_CURSOR_Y) xxxxxxxxh Page 333

06Ch RO DC Line Count/Status (DC_LINE_CNT/STATUS) xxxxxxxxh Page 333

Palette Access and FIFO Diagnostic Registers

070h R/W DC Palette Address (DC_PAL_ADDRESS) xxxxxxxxh Page 335

074h R/W DC Palette Data (DC_PAL_DATA) xxxxxxxxh Page 336

078h R/W DC Display FIFO Diagnostic (DC_DFIFO_DIAG) xxxxxxxxh Page 336

07Ch R/W DC Compression FIFO Diagnostic

(DC_CFIFO_DIAG)

xxxxxxxxh Page 337

Video Downscaling Registers

080h R/W DC Video Downscaling Delta (DC_VID_DS_DELTA) 00000000h Page 338

GLIU0 Control Registers

084h R/W DC GLIU0 Memory Offset

(DC_GLIU0_MEM_OFFSET)

00000000h Page 339

088h R/W DC Dirty/Valid RAM Control (DC_DV_CTL) 00000000h Page 339

Table 6-47. DC Configuration Control Register Summary (Continued)

DC

Memory

Offset Type Register Name Reset Value Reference