650 AMD Geode™ LX Processors Data Book

Instruction Set

33234H

Exceptions

#UD If current privilege level is not 0, or the DMM_INST_EN = 0 and if the processor is not in SMM and if the processor

is not in DMM.

Notes

Data address breakpoints on DMM header addresses are ignored during the execution of the RSM instruction.

The RDM instruction does not check the values that it reads from the DMM header for validity.

The RDM instruction sets the current privilege level to the SS DPL value read from the DMM header.

If a RDM restores the processor to real mode, the VM bit of the EFlags register is cleared regardless of the state of the VM

bit in the EFlags value of the DMM header.

If RDM restores the processor to a privilege level that is not 3, then the VM bit of the EFlags register is cleared, regardless

of the contents of the VM bit in the EFlags value of the DMM header.

8.3.4.5 RSDC - Restore Segment Register and Descriptor

Operation

Description

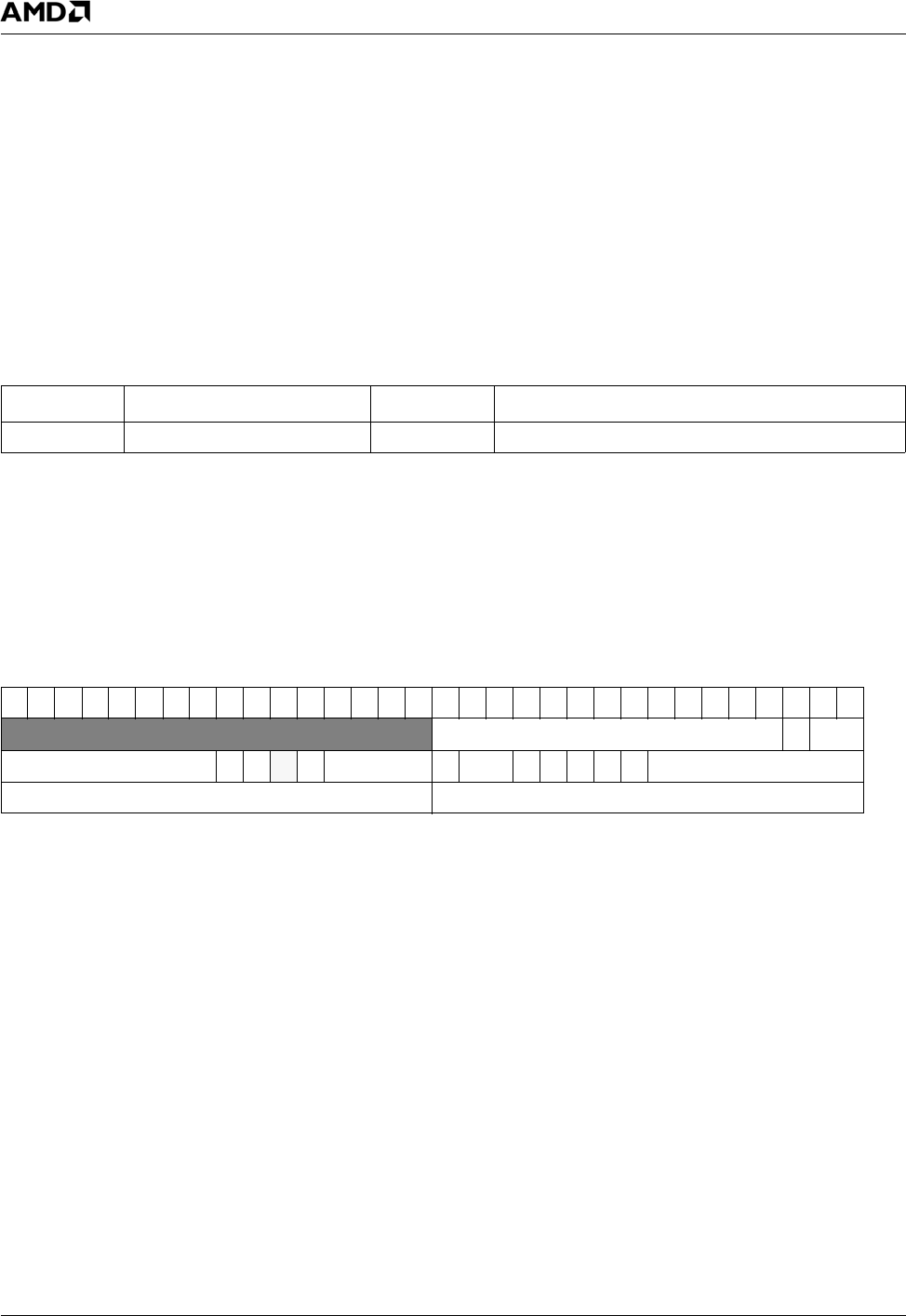

Restore the specified segment descriptor (either DS, ES, FS, GS, SS, or CS) from memory. Below is the format of the

descriptor contents in memory.

Flags Affected

None.

Exceptions

#UD If current privilege level is not 0, or the SMM_INST_EN = 0 and if the processor is not in SMM and if the processor

is not in DMM.

Notes

The reg field within the mod r/m byte specifies which segment’s register and descriptor should be restored. Reg fields of 0,

1, 2, 3, 4, and 5 specify the ES, CS, SS, DS, FS, and GS selectors respectively. The RSDC instruction is not recognized if

the reg field is 6 or 7.

The RSDC instruction does not check its memory operand for validity. Care should be taken to always load valid data into

segment registers.

A RSDC CS instruction’s alteration of the CS base does not take affect until the execution of the next non-sequential

instruction or pipeline flush. A pipeline flush could be caused by an external suspend, an external debug stall, or an SMC

snoop hit. A RSDC CS instruction’s alteration of the CS limit takes affect immediately.

A RSDC SS instruction alters the CPL to the DPL value. If the executable bit (X) is set, then the CS becomes unwritable.

External interrupts, single-step traps, and debug exceptions are not taken between a RSDC CS instruction and the RSLDT

instruction (Section 8.3.4.6 on page 651).

Opcode Instruction Clocks Description

0F 79 /r RSDC sr, m80 11 Restore descriptor from memory

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

SELECTOR[15:3] TI RPL +8

BASE[31:24] G B

0 V LIMIT[19:16] 1 DPL 1 X E W A BASE[23:16] +4

BASE[15:0] LIMIT[15:0] +0

IF (CPL<>0 OR (SMM_INST_EN=0 AND SMM=0 AND DMM=0))

#UD;

ELSE

SEG.DESCR <= MEM80;