454 AMD Geode™ LX Processors Data Book

Video Processor Register Descriptions

33234H

6.8.3.45 Power Management (PM)

19 MCS Color/Mono Select. Selects color or monochrome LCD panel.

0: Color.

1: Monochrome.

18:16 PIXF Pixel Output Format. These bits define the pixel output format. The selection of the

pixel output format determines how the pixel data is formatted before being sent on to the

DRGB pins. These settings also determine the SHFCLK frequency for the specific panel.

000: Up to 24-bit TFT panel with one pixel per clock.

SHFCLK = DOTCLK.

001: 18/24-bit TFT XGA panel with two pixels per clock.

SHFCLK = 1/2 of DOTCLK.

010, 011, 100, 101, 110, and 111: Reserved.

15:0 RSVD Reserved. These bits are not defined.

FP Memory Offset 410h

Typ e R /W

Reset Value 00000000_00000002h

PT2 Bit Descriptions (Continued)

Bit Name Description

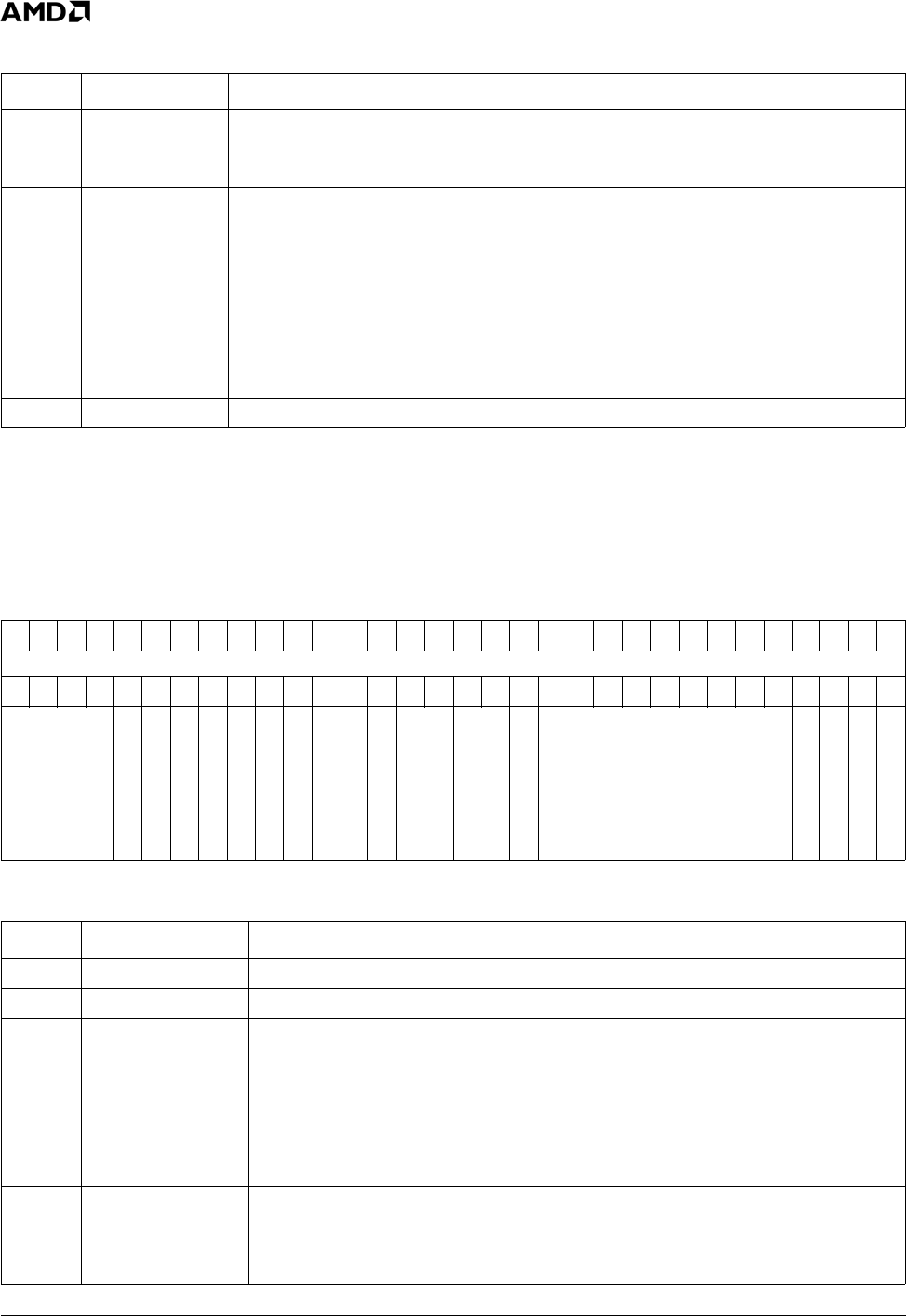

PM Register Map

63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32

RSVD

313029282726252423222120191817161514131211109876543210

SP

PWR_SEQ_SEL

PNL_PWR_SIM

D

P

PUB2

PUB1

PUB0

PD2

PD1

PD0

HDEL VDEL

SINV

SP

PANEL_PWR_UP

PANEL_PWR_DOWN

PANE L_O FF

PANEL_ON

PM Bit Descriptions

Bit Name Description

63:32 RSVD (RO) Reserved (Read Only). Reads back as 0.

31:28 SP Spares. Read/write; no function.

27 PWR_SEQ_SEL Power Sequence Select. Selects whether to use internal or external power

sequence. The power sequence controls the order in which VDDEN, the data and

control signals, and the backlight control signal DISPEN become active during power

up, and inactive during power down.

0: Use internal power sequencing (timing is controlled by bits [24:18]).

1: Use external power sequencing.

Must be written to 0.

26 PNL_PWR_SIM Panel Power Sequence Test Mode. This bit should always be set to 0.

For simulating the model of the panel power sequence logic, this bit may be set to 1. It

connects the 14 MHz reference clock to the 32 Hz panel power sequence clock for

faster simulations. The hardware will not function properly if this bit is set to 1.