AMD Geode™ LX Processors Data Book 647

Instruction Set

33234H

Description

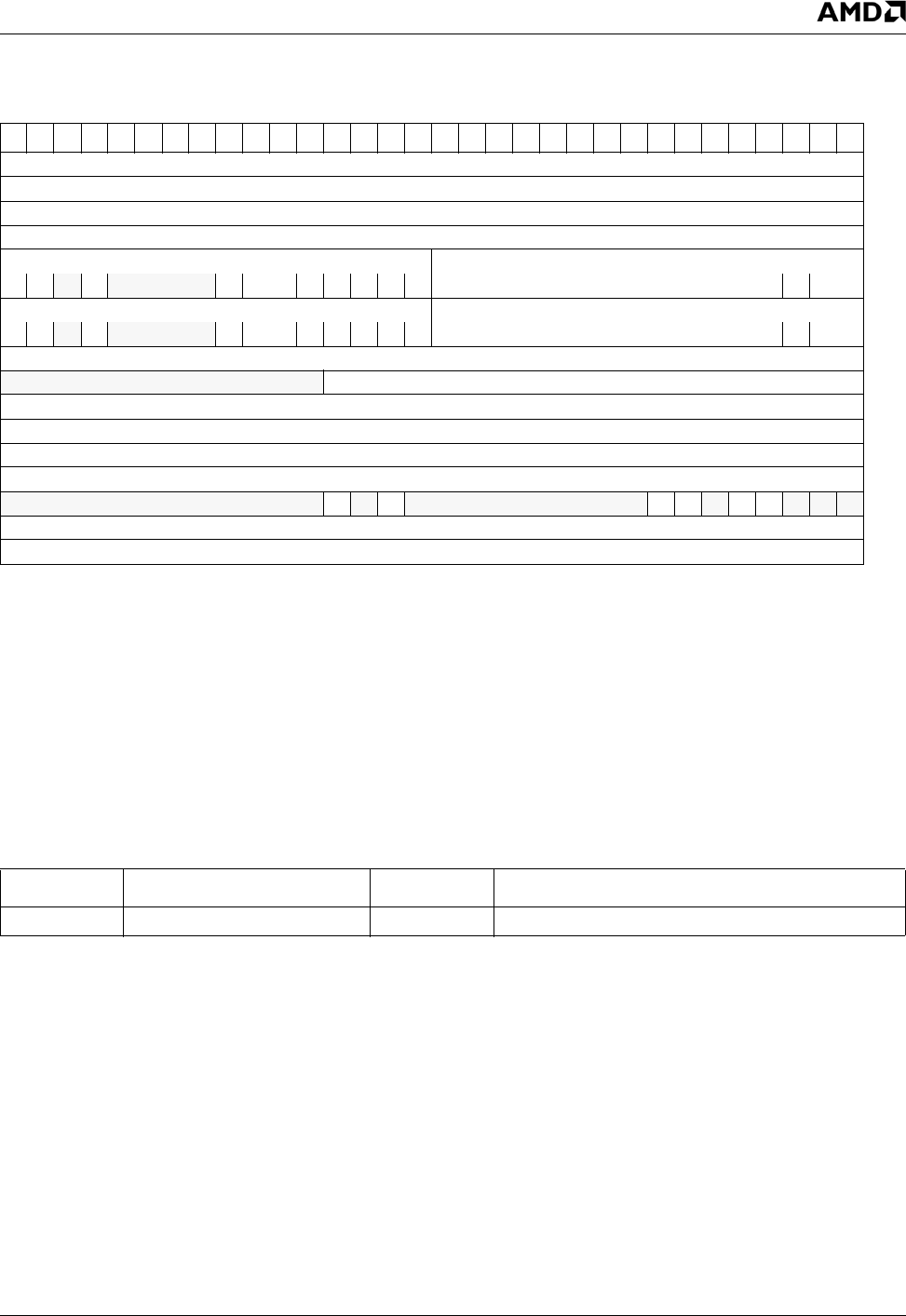

The DMINT instruction saves portions of the processors state to the Debug Management Mode (DMM) header, alters the

processors state for DMM, enters DMM, and then calls the DMM mode handler. Below is the format of the DMM header.

Flags Affected

All EFlags are returned to their reset values.

Exceptions

#UD If current privilege level is not 0, or the DMM_INST_EN = 0 and if the processor is not in SMM and if the pro-

cessor is not in DMM.

Notes

Data address breakpoints on DMM header addresses that occur when executing the DMINT instruction are ignored.

The DMINT instruction clears the V, X, and H bits of the DMM header. DMINT sets the S bit of the DMM header. The

NEXT_IP failed of the DMM header will point to the instruction after the DMINT.

8.3.4.2 ICEBP - Call Debug Exception Handler

Operation

Same as an INT 1 instruction.

Description

The ICEBP instruction generates a call to the Debug exception handler. It’s advantage over the INT 1 instruction is that it is

a single byte opcode.

Flags Affected

The EFlags are pushed to the stack, and may then be modified before the debug exception handler is called. The EFlags

may be restored by the debug exception handler’s IRET.

Notes

Debuggers should not insert ICEBP instruction immediately after an instruction that alters the stack segment (MOV_SS).

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

DR6 -4

DR7 -8

XDR6 -C

XDR7 -10

SS FLAGS SS SELECTOR -14

GB

0Av 0 1 DPL 1 0 E W A INDEX TI RPL

CS FLAGS CS SELECTOR -18

GD

0Av 01DPL11C

f

R A INDEX TI RPL

CS BASE -1C

0 CS LIMIT -20

CURRENT_IP -24

NEXT_IP -28

CR0 -2C

EFLAGS -30

0c

w

0c

r

0VX0HS0 0 0-34

TEMP6 -38

AC TEMP0 -3C

Opcode Instruction Clocks Description

F1 ICEBP 29+ Call Debug Exception Handler