368 AMD Geode™ LX Processors Data Book

Display Controller Register Descriptions

33234H

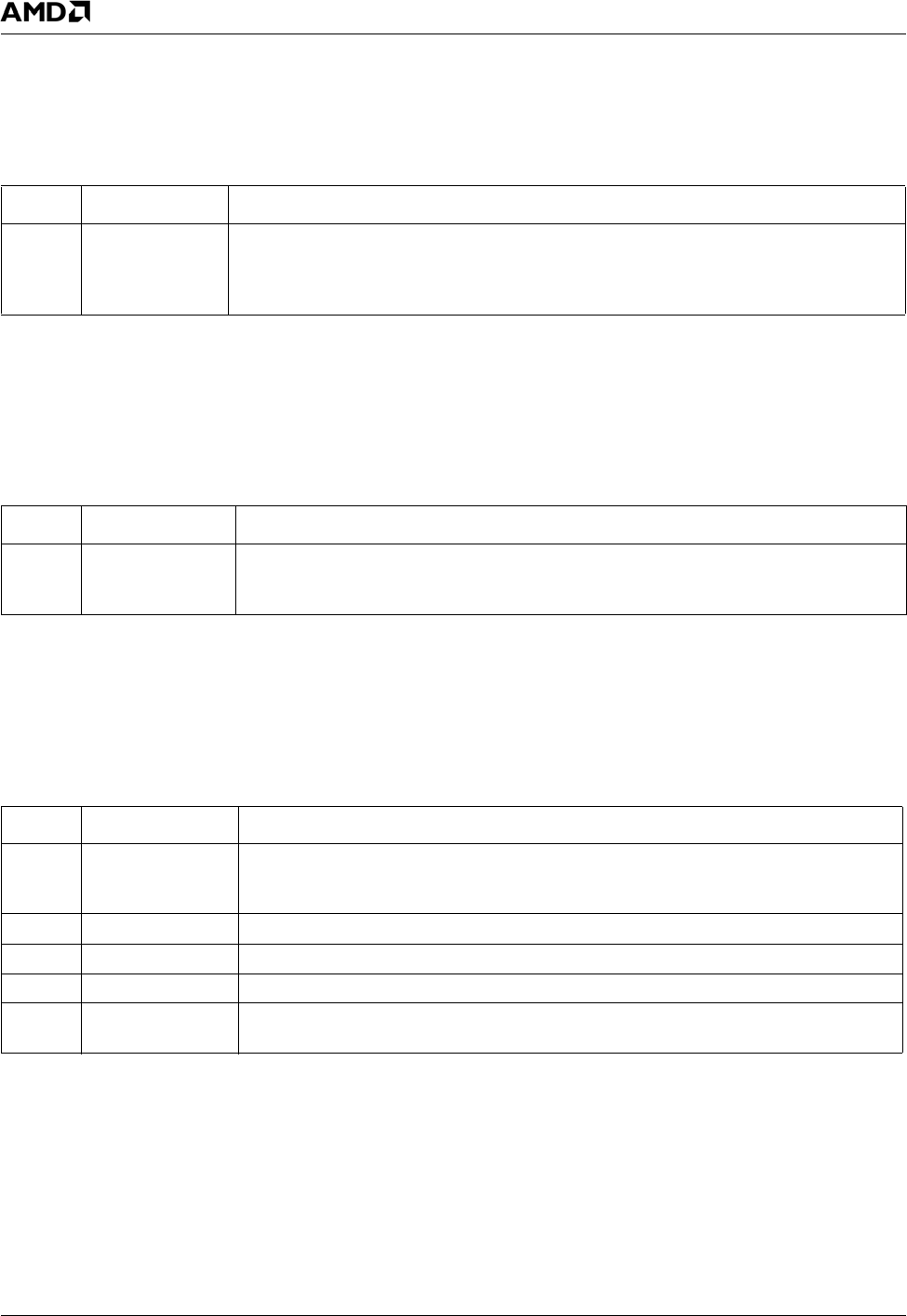

6.6.19.18 Cursor Location Low

6.6.19.19 Vertical Sync Start

6.6.19.20 Vertical Sync End

Index 0Fh

Typ e R /W

Reset Value 00h

Cursor Location Low Register Bit Descriptions

Bit Name Description

7:0 CURS_LOW Cursor Location Register Bits [7:0]. Together with the register (CURS_HI, Index

0Eh[7:0]), this value specifies the frame buffer address where the cursor is displayed in

text mode. The cursor will appear at the character whose memory address corresponds

to this value.

Index 10h

Typ e R /W

Reset Value 00h

Vertical Sync Start Register Bit Descriptions

Bit Name Description

7:0 VERT_SYNC_ST Vertical Sync Start Register Bits [7:0]. This value specifies the scan line number

where the vertical sync signal will go active. This is a 10-bit value. Bits 9 and 8 are in the

Overflow register (Index 07h[7,2]).

Index 11h

Typ e R /W

Reset Value 00h

Vertical Sync End Register Bit Descriptions

Bit Name Description

7WR_PROT Write-Protect Registers. This bit is used to prevent old EGA programs from writing

invalid values to the VGA horizontal timing registers. The LINE_COMP8 (Index 07h[4])

is not protected by this bit.

6 RSVD Not Implemented. (Refresh Cycle Select)

5 RSVD Not Implemented. (Enable Vertical Interrupt)

4 RSVD Not Implemented.(Clear Vertical Interrupt)

3:0 V_SYNC_END Vertical Sync End Register Bits [3:0]. This field represents the low four bits of a com-

pare value that specifies which scan line that the vertical sync signal goes inactive.