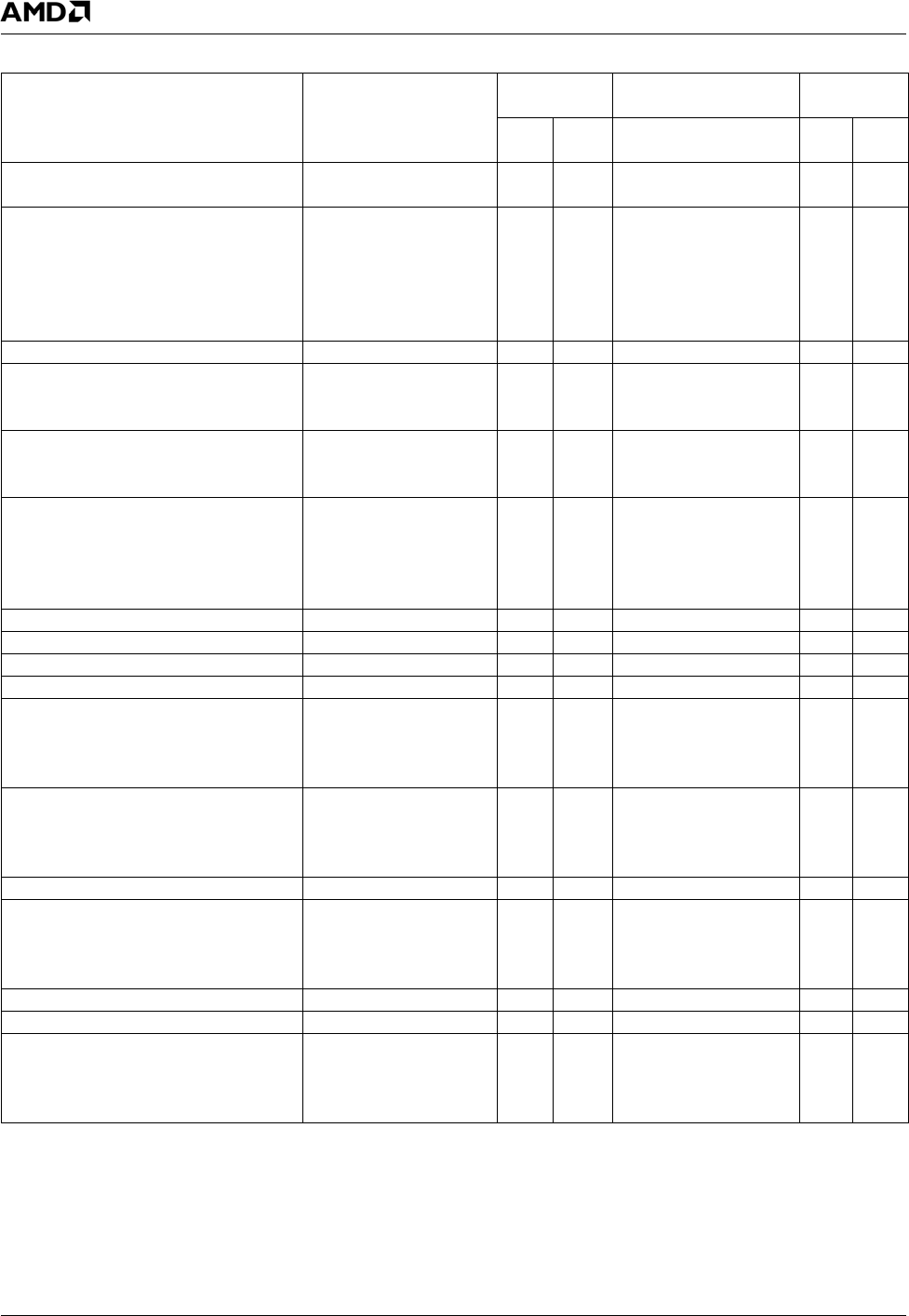

636 AMD Geode™ LX Processors Data Book

Instruction Set

33234H

CMOVNS Move if Not Sign 0F 49 [mod reg r/m] 1 1 --------- r

Register, Register/Memory

CMP Compare Integers x---xxxxx b h

Register to Register 3 [10dw] [11 reg r/m] 1 1

Register to Memory 3 [101w] [mod reg r/m] 1 1

Memory to Register 3 [100w] [mod reg r/m] 1 1

Immediate to Register/Memory 8 [00sw] [mod 111 r/m] ### 1 1

Immediate to Accumulator 3 [110w] ### 1 1

CMPS Compare String A [011w] 6 6 x---xxxxx b h

CMPXCHG Compare and Exchange x---xxxxx

Register1, Register2 0F B [000w] [11 reg2 reg1] 4 4

Memory, Register 0F B [000w] [mod reg r/m] 4-5 4-5

CMPXCHG8B Compare and Exchange 8 Bytes 0F C7 [mod 001 r/m] ---------

If {EDX,EAX} == DST 10 10

If {EDX,EAX} != DST 12 12

CPUID CPU Identification 0F A2 ---------

If EAX <= 1 13 13

If 1 < EAX < 2

31

10 10

If 2

31

<= EAX <= (2

31

+6) 14 14

If EAX > (2

31

+6) 11 11

CWD Convert Word to Doubleword 99 1 1 ---------

CWDE Convert Word to Doubleword Extended 98 3 3 ---------

DAA Decimal Adjust AL after Addition 27 2 2 ----xxxxx

DAS Decimal Adjust AL after Subtraction 2F 2 2 ----xxxxx

DEC Decrement by 1 x---xxxx- b h

Register/Memory Byte FE [mod 001 r/m] 1 1

Register/Memory Word/DWord FF [mod 001 r/m] 1 1

Register (short form) 4 [1 reg] 1 1

DIV Unsigned Divide ----xxuu-

Accumulator by Register/Memory

Divisor: Byte

Word

Doubleword

F [011w] [mod 110 r/m]

15

23

7-39

15

23

7-39

b,e e,h

DMINT Enter Debug Management Mode 0F 39 48-50 50-52 000000000 s, u s, u

ENTER Enter New Stack Frame C8 ##,# ---------

Level = 0 77 bh

Level = 1 13 13

Level (L) > 1 15+21 15+21

HLT Halt F4 13+ 13+ --------- l

ICEBP Call Debug Exception Handler F1 29+ 29+ --x0----- u u

IDIV Integer (Signed) Divide F [011w] [mod 111 r/m] ----xxuu- b,e e,h

Accumulator by Register/Memory

Divisor: Byte

Word

Doubleword

16

24

40

16

24

7-40

Table 8-26. Processor Core Instruction Set (Continued)

Instruction Opcode

Clock Count

(Reg/Cache Hit) Flags

Notes

Real

Mode

Prot’d

Mode

ODI TSZ APC

FFFFFFFFF

Real

Mode

Prot’d

Mode