AMD Geode™ LX Processors Data Book 317

Display Controller Register Descriptions

33234H

6.6.3.3 DC Display Configuration (DC_DISPLAY_CFG)

This register contains configuration bits for controlling the various display functions of the DC.

Unless otherwise noted, settings written to this register do not take effect until the start of the following frame or interlaced

field.

DC Memory Offset 008h

Typ e R /W

Reset Value 00000000h

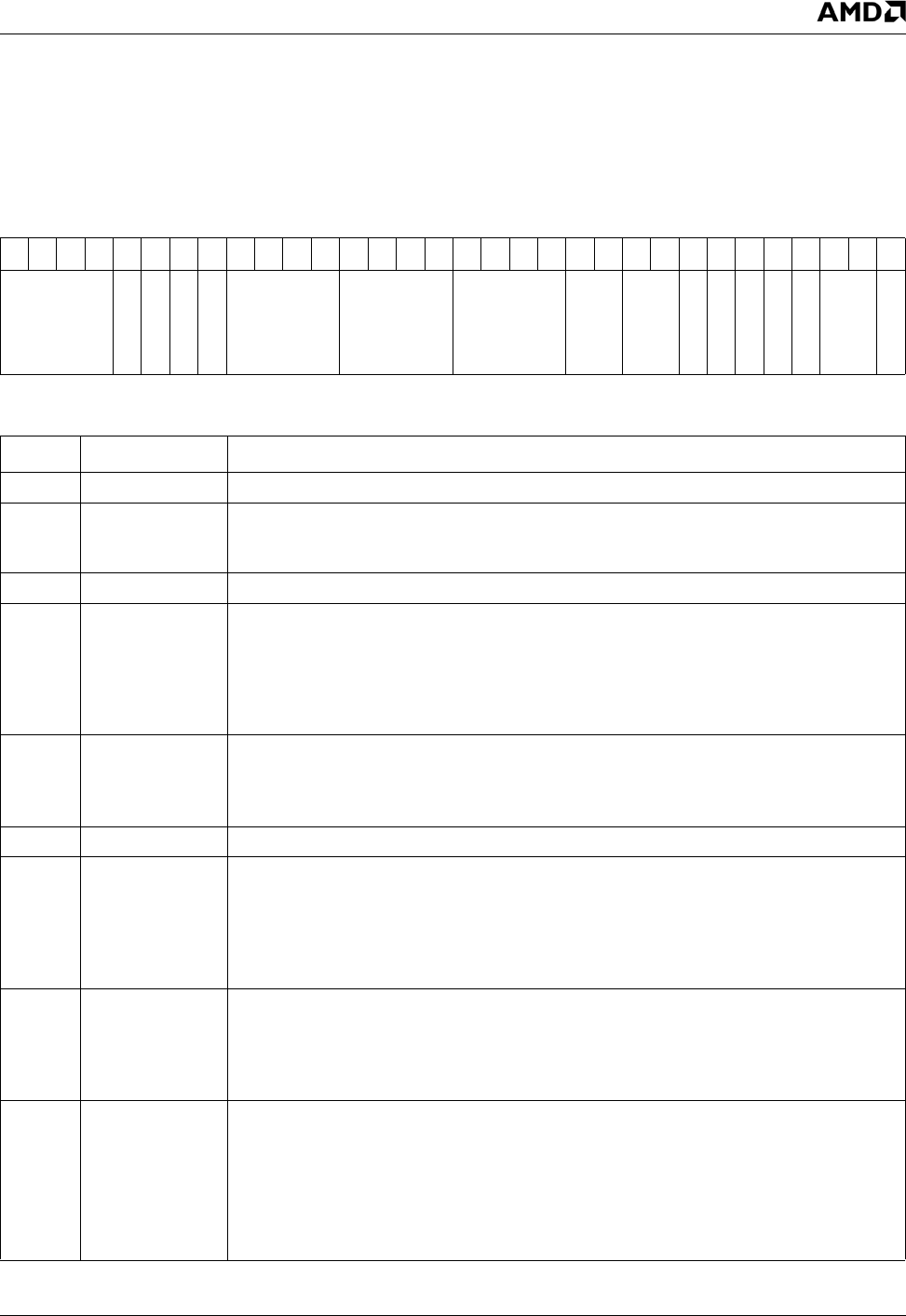

DC_DISPLAY_CFG Register Map

313029282726252423222120191817161514131211109876543210

RSVD

VISL

RSVD

PALB

DCEN

RSVD VFHPEL VFHPSL

16BPP_MODE

DISP_MODE

RSVD

TRUP

RSVD

VDEN

GDEN

RSVD

TGEN

DC_DISPLAY_CFG Bit Descriptions

Bit Name Description

31:28 RSVD Reserved.

27 VISL Vertical Interrupt Select. Effective immediately.

0: SMI generated at start of vertical blank when VIEN is enabled (bit 5 = 1).

1: SMI generated at end of vertical sync when VIEN is enabled (bit 5 = 1).

26 RSVD Reserved.

25 PALB PAL Bypass.

0: Graphics data is routed through palette RAM in 16, 24, and 32-bpp display modes.

1: Graphics data bypasses palette RAM in 16, 24, and 32-bpp display modes. While con-

figured in this mode, 2-bpp cursor and border overlays are supported, but the palette

entries for these items must be modified. See Section 6.6.7.1 on page 335 for more

information.

24 DCEN Display Center.

0: Normal active portion of scan line is qualified with DISPEN (ball AE4).

1: Border and active portions of scan line are qualified with DISPEN. This enables cen-

tering the display for flat panels.

23:20 RSVD Reserved.

19:16 VFHPEL Video-FIFO High Priority End Level. This field specifies the depth of the video FIFO (in

multiples of 64 bytes) at which a high priority request previously issued to the memory

controller for video data will end. This field should always be non-zero and should be

larger than the start level. Note that the settings in the DC_ARB_CFG register (DC Mem-

ory Offset 00Ch) can also affect the priority of requests. This field should be set to 0 if

video overlay is disabled.

15:12 VFHPSL Video-FIFO High Priority Start Level. This field specifies the depth of the video FIFO

(in multiples of 64 bytes) at which a high priority request is sent to the memory controller

to fill up the video FIFO. This field should always be non-zero and should be less than the

high-priority end level. Note that the settings in the DC_ARB_CFG register (DC Memory

Offset 00Ch) can also affect the priority of requests.

11:10 16BPP_MODE Per-Pixel Mode. Based on the number of bits per pixel (DISP_MODE bits [9:8] must

equal 01), this determines how those bits are allocated to color and alpha information:

For 16-bpp display format:

00: 16-bpp (RGB 5:6:5)

01: 15-bpp (RGB 5:5:5)

10: XRGB (ARGB 4:4:4)

11: Reserved