AMD Geode™ LX Processors Data Book 433

Video Processor Register Descriptions

33234H

6.8.3.16 CRC Signature (CRC)

VP Memory Offset 088h

Typ e R /W

Reset Value 00000000_00000000h

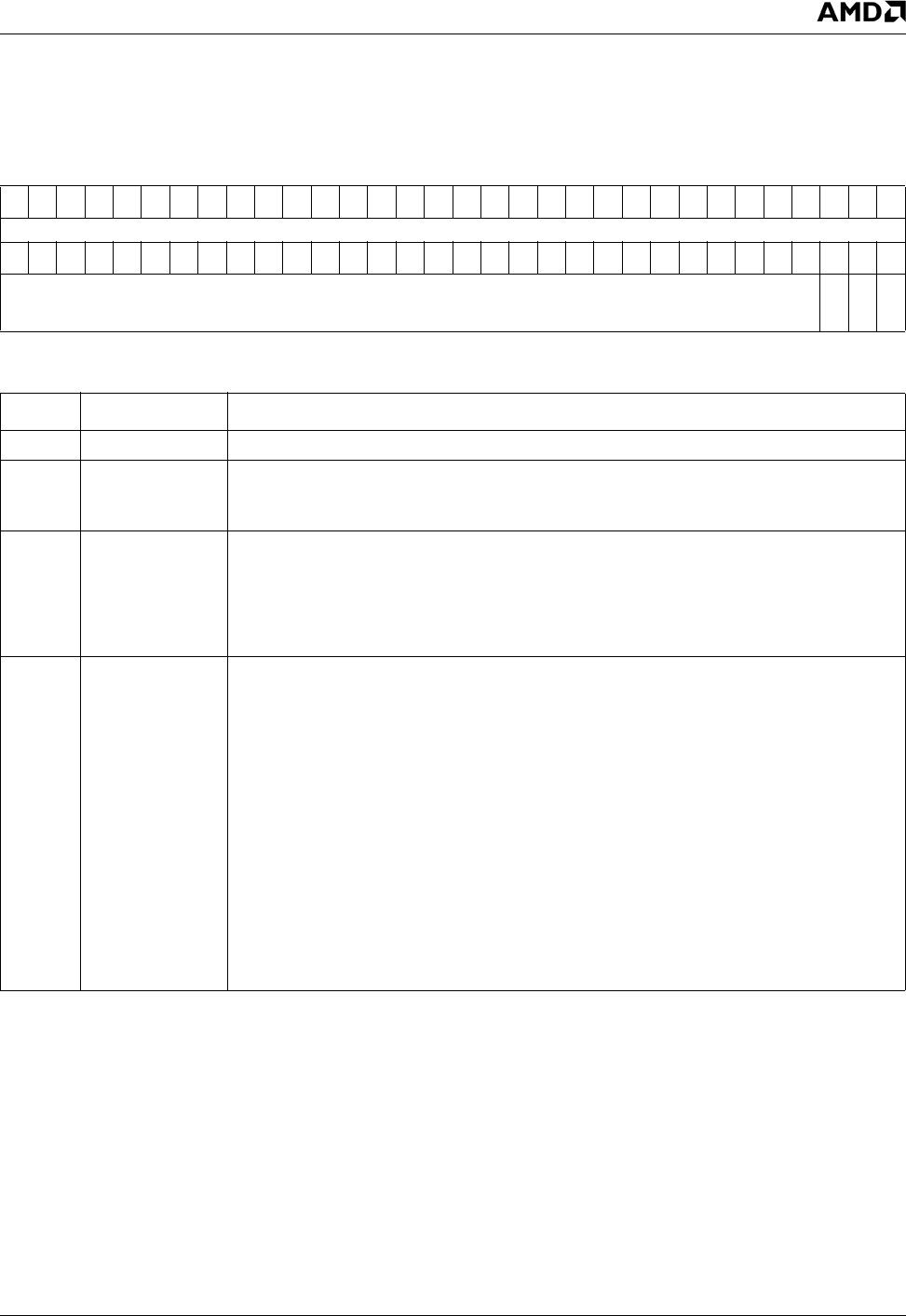

CRC Register Map

63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32

RSVD

313029282726252423222120191817161514131211109876543210

RSVD

SIGVAL

SIGFR

SIGEN

CRC Bit Descriptions

Bit Name Description

63:3 RSVD (RO) Reserved (Read Only). Reads back as 0.

2 SIGVAL (RO) Signature Valid (Read Only). If this bit is set, the signature operation has completed

and the signature may be safely read from the 32-Bit CRC Signature Register (VP Mem-

ory Offset 090h).

1SIGFR Signature Free Run.

0: Disable. (Default). If this bit was previously set to 1, the signature process will stop at

the end of the current frame (i.e., at the next falling edge of VSYNC).

1: Enable. If SIGNEN (bit 0) is set to 1, the signature register captures data continuously

across multiple frames.

0SIGEN Signature Enable.

0: Disable. The SIGVAL (bits [31:8]) is reset to 000001h in 24-bit mode or 000000h in 32-

bit mode and held (no capture). (Default)

1: Enable. When this bit is set to 1, the next falling edge of VSYNC is counted as the start

of the frame to be used for CRC checking with each pixel clock beginning with the next

VSYNC.

If SIGFR (bit 1) is set to 1, the signature register captures the pixel data signature con-

tinuously across multiple frames.

If SIGFR (bit 1) is cleared to 0, a signature is captured one frame at a time, starting

from the next falling VSYNC.

After a signature capture is complete, the SIGVAL (bit 2) can be read to determine the

CRC check status. In 32-bit CRC mode, the full 32-bit signature can be read from the 32-

Bit CRC Signature (VP Memory Offset 090h[31:0]). Then proceed to reset SIGEN, which

initializes SIGVAL as an essential preparation for the next round of CRC checks.