632 AMD Geode™ LX Processors Data Book

Instruction Set

33234H

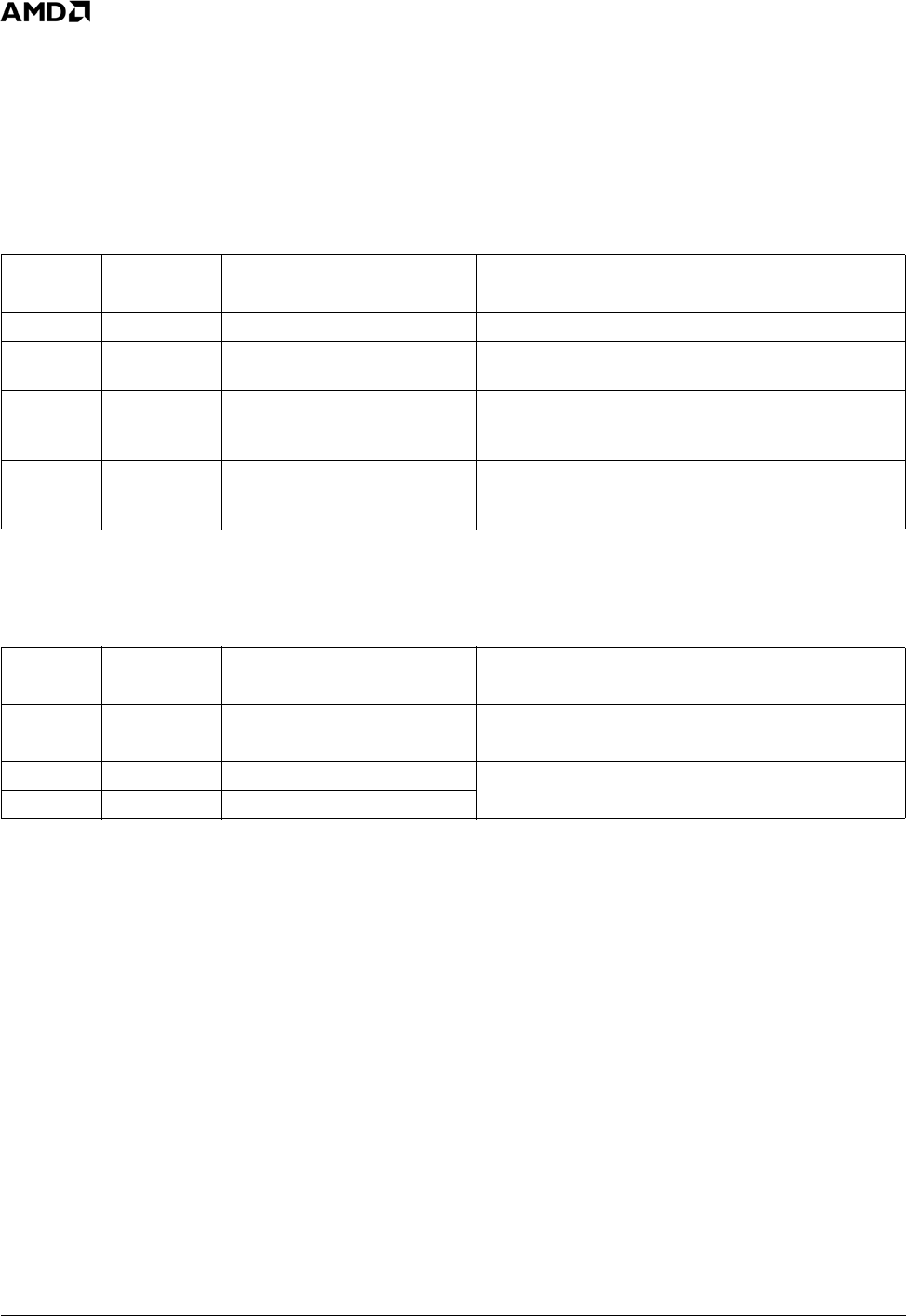

8.2.2.4 CPUID Instruction with EAX = 80000005h

Extended function 80000005h (EAX = 80000005h) of the CPUID instruction returns information on the internal L1 cache

and TLB structures. They are used for reporting purposes only. See Table 8-23 for returned contents.

8.2.2.5 CPUID Instruction with EAX = 80000006h

Extended function 80000006h (EAX = 80000006h) of the CPUID instruction returns information on the internal L2 cache

and TLB structures. See Table 8-24 on page 632 for returned contents.

.

Table 8-23. CPUID Instruction with EAX = 80000005h

Register

Returned

Contents Description Comment

EAX 00000000h 4 MB L1 TLB Information Indicates no 4 MB L1 TLB.

EBX FF10FF10h 4 KB L1 TLB Information Decodes to eight fully associative code TLB and eight

fully associative data TLB entries.

ECX 40100120h L1 Data Cache Information Indicates 16 KB four-way associative with 32-byte lines

for data cache. These encodings follow the AMD report-

ing method.

EDX 40100120h L1 Code Cache Information Indicates 16 KB four-way associative with 32-byte lines

for code cache. These encodings follow the AMD report-

ing method.

Table 8-24. CPUID Instruction with EAX = 80000006h

Register

Returned

Contents Description Comment

EAX 0000F004h L2 TLB Information Two-way associative 64 entry code and data combined

TLB.

EBX 00002040h L2 TLB Information

ECX 00804120h L2 Code Cache Information Indicates no L2 cache.

EDX 00000000h L2 Data Cache Information