AMD Geode™ LX Processors Data Book 423

Video Processor Register Descriptions

33234H

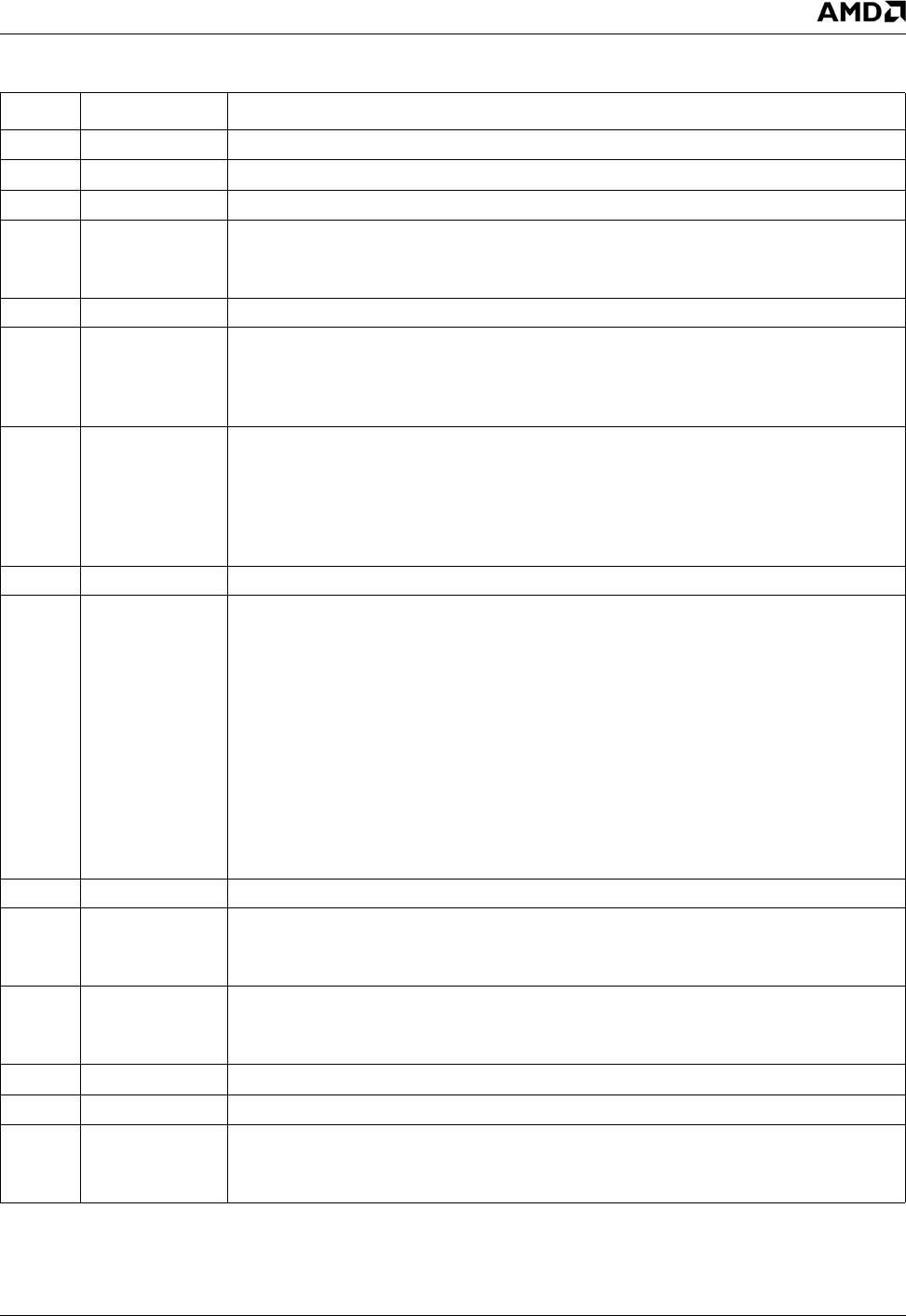

DCFG Bit Descriptions

Bit Name Description

63:32 RSVD (RO) Reserved (Read Only). Reads back as 0.

31:28 SP Spares. Bits are read/write, but have no function.

27 RSVD (RO) Reserved (Read Only). Reads back as 0.

26 DAC_VREF Select CRT DAC VREF. Allows use of an external voltage reference for CRT DAC.

0: Disable external VREF.

1: Use external VREF.

25:22 RSVD (RO) Reserved (Read Only). Reads back as 0.

21 GV_GAM Graphics/Video Gamma. Selects whether the graphic or video data should pass

through the Gamma Correction RAM.

0: Graphic data passes through the Gamma Correction RAM.

1: Video data passes through the Gamma Correction RAM.

20 VG_CK Video/Graphics Color Key Select. Selects whether the graphic data is used for color-

keying or the video data is used for chroma-keying. Note that this affects the final output

with or without blending enabled. See Figure 6-31 on page 438 and Table 6-64 on page

439 for details.

0: Graphic data is compared to the color key.

1: Video data is compared to the chroma key.

19:17 RSVD (RO) Reserved (Read Only). Reads back as 0.

16:14 CRT_SYNC

_SKW

CRT Sync Skew. Represents the number of pixel clocks to skew the horizontal and ver-

tical sync that are sent to the CRT. This field should be programmed to 100 (i.e., baseline

sync is not moved) as the baseline. Via this register, the sync can be moved forward

(later) or backward (earlier) relative to the pixel data. This register can be used to com-

pensate for possible delay of pixel data being processed via the Video Processor.

000: Sync moved 4 clocks backward.

001: Sync moved 3 clocks backward.

010: Sync moved 2 clocks backward.

011: Sync moved 1 clock backward.

100: Baseline sync is not moved. (Default)

101: Sync moved 1 clock forward.

110: Sync moved 2 clocks forward.

111: Sync moved 3 clocks forward.

13:10 SP Spares. Bits are read/write, but have no function.

9 CRT_VSYNC

_POL

CRT Vertical Synchronization Polarity. Selects the polarity for CRT vertical sync.

0: CRT vertical sync is normally low and is set high during the sync interval.

1: CRT vertical sync is normally high and is set low during the sync interval

8CRT_HSYNC

_POL

CRT Horizontal Synchronization Polarity. Selects the polarity for CRT horizontal sync.

0: CRT horizontal sync is normally low and is set high during sync interval.

1: CRT horizontal sync is normally high and is set low during sync interval.

7:6 RSVD (RO) Reserved (Read Only). Reads back as 0.

5:4 SP Spares. Bits are read/write, but have no function.

3 DAC_BL_EN DAC Blank Enable. Controls blanking of the CRT DACs.

0: DACs are constantly blanked.

1: DACs are blanked normally (i.e., during horizontal and vertical blank).