560 AMD Geode™ LX Processors Data Book

GeodeLink™ Control Processor Register Descriptions

33234H

6.14.2.17 GLCP Control (GLCP_CNT)

This register is used in conjunction with GLIU1 Power Management. I/O writes, which include the lowest byte of this regis-

ter, may trigger an SMI if GLD_MSR_SMI (MSR 4C002002h) is configured appropriately. MSR writes do not cause SMIs.

The throttle sequence starts after the delay specified by GLCP_TH_SD (MSR 4C00001Ch), which can allow for SMI han-

dling time or any other preparations. Throttling is temporarily stopped in IRQ, SSMI, ASMI, or DMI. NMI and system sleep

(C2) always clear THT_EN (bit 4).

6.14.2.18 GLCP Level 2 (GLCP_LVL2)

This register has no writable bits. I/O reads to the lower byte of this register (with or without reading the other three bytes)

return 0 and cause the system to enter “C2 processor state” as defined by the GLIU1 power management spec; that is, sus-

pend the processor. I/O reads to the lower byte of this register may trigger an SMI if GLD_MSR_SMI (MSR 4C002002h) is

configured appropriately. Note that the suspend starts after a delay specified by GLCP_TH_SD (MSR 4C00001Ch), which

can allow for SMI handling or any other preparations. P_LVL2_IN (MSR 4C00001Ch[12]) can abort the suspend operation.

MSR reads to this register return 0, but perform no further action.

MSR Address 4C000018h

Type R/W - I/O Offset 00h

Reset Value 00000000_000000Fh

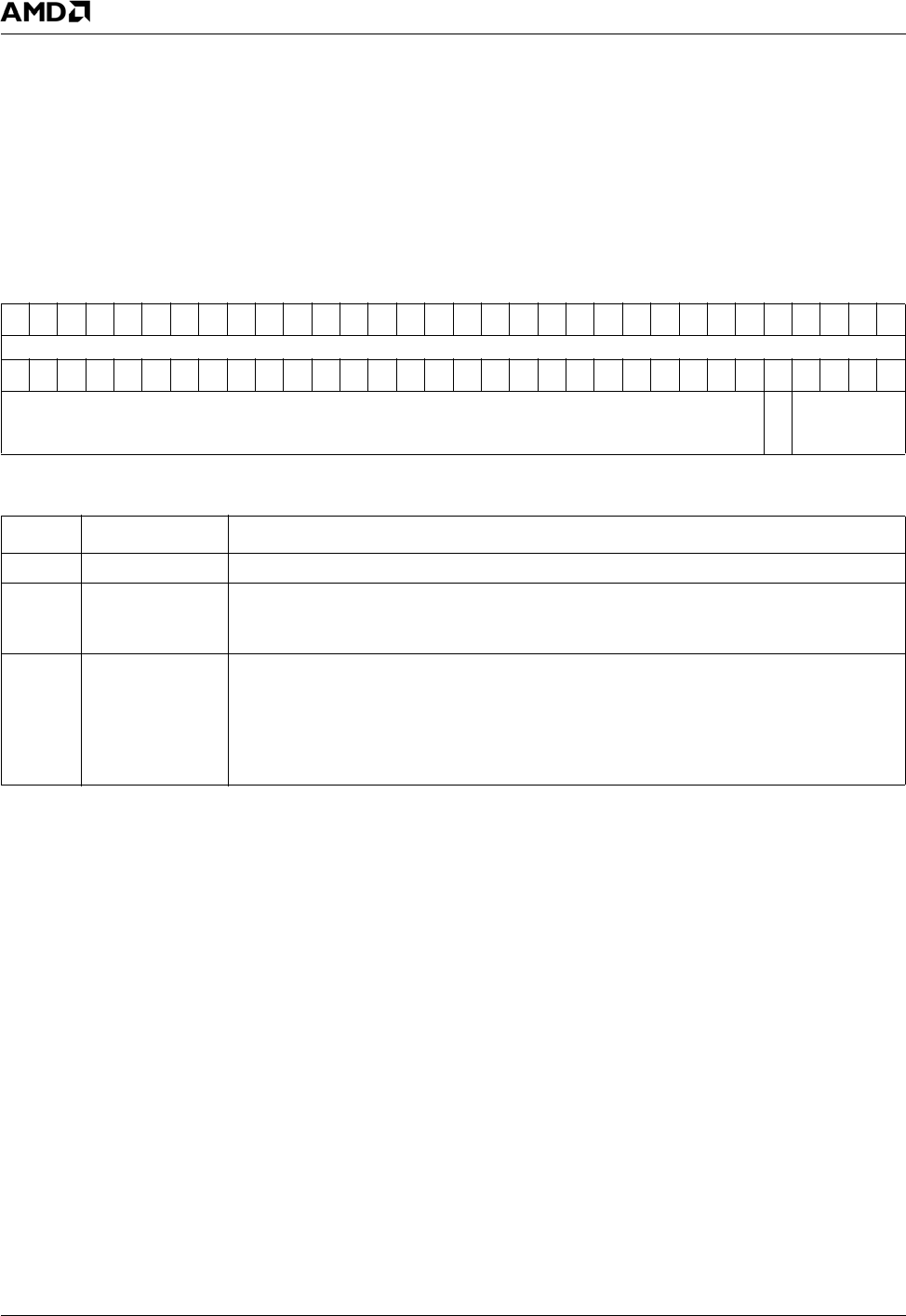

GLCP_CNT Register Map

63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32

RSVD

313029282726252423222120191817161514131211109876543210

RSVD

THT_EN

CLK_VAL

GLCP_CNT Bit Descriptions

Bit Name Description

63:5 RSVD Reserved. Write as read.

4THT_EN Throttle Enable. When high, enables throttling of processor for power management.

This bit is always cleared by an NMI to the processor or when system sleep initiates, it

may clear from an SMI or IRQ depending on GLCP_TH_OD (MSR 4C00001Eh) settings.

3:0 CLK_VAL Clock Throttling Value. The value 0000 is reserved and should not be used. The value

0001 yields the most throttling while the value 1111 has the effect of no throttling (1111 is

the reset value). Reads return value written. THT_EN (bit 4) must be low to change the

value of CLK_VAL. See also GLCP_TH_SF (MSR 4C00001Dh). During processor throt-

tling, processor suspend is applied the amount of time of “(15-CLK_VAL)*GLCP_TH_SF”

and then removed the amount of time of “CLK_VAL*GLCP_TH_SF”.

MSR Address 4C000019h

Type R/W - I/O Offset 04h

Reset Value 00000000_00000000h