582 AMD Geode™ LX Processors Data Book

GeodeLink™ PCI Bridge Register Descriptions

33234H

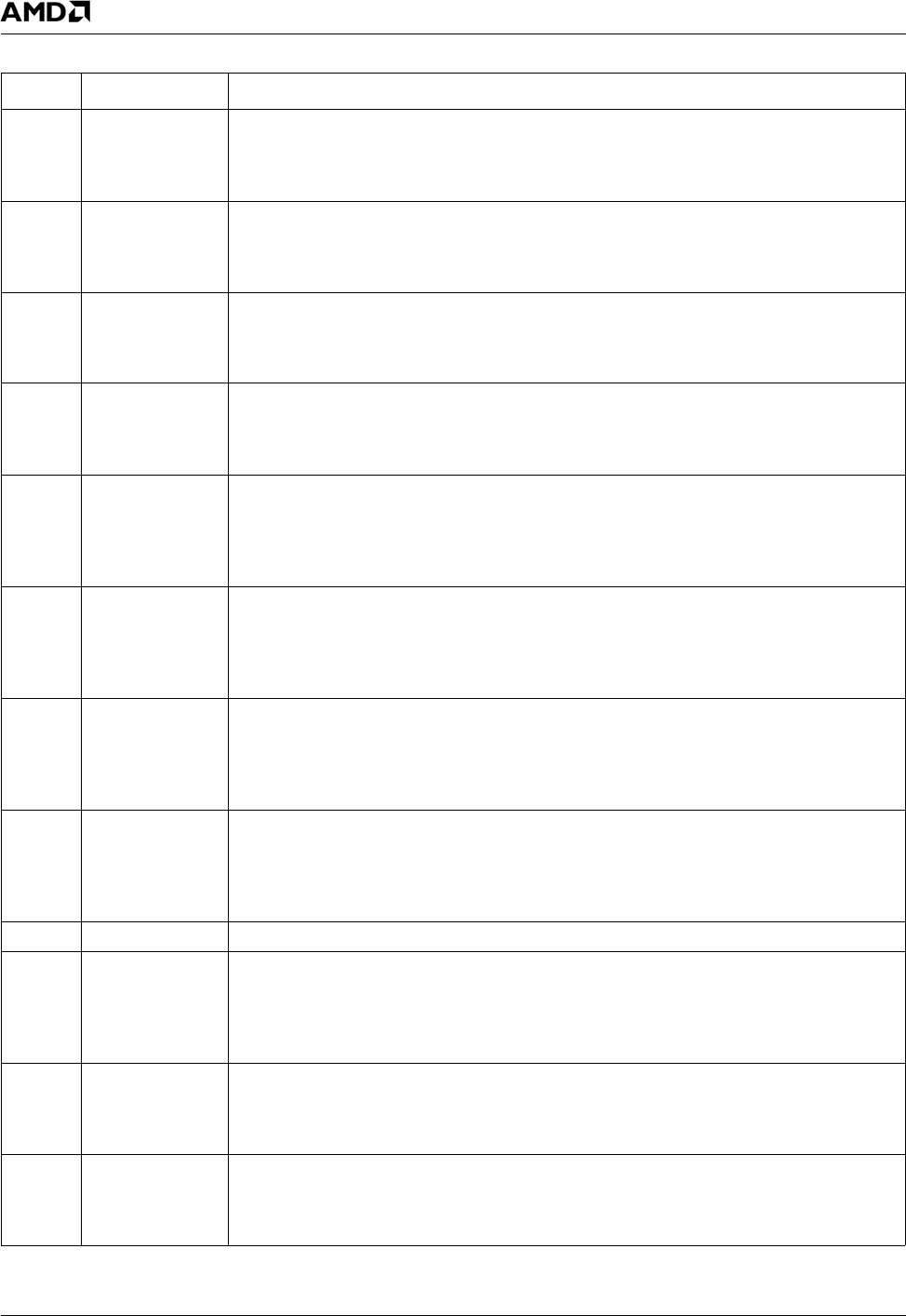

GLPCI_ARB Bit Definitions

Bit Name Description

63:60 CR CPU Repeat. Controls the number of consecutive grants given to the CPU before rotat-

ing to the next requestor. This is only valid if there is a non-zero value for the CPU Hold-

Grant control (CH, bits [47:44]). This may be overidden by either OV2, OV1 or OV0 (bits

[22:20]). It is also ignored if the CPRE (bit 11) is cleared.

59:56 R2 Request Repeat 2. Controls the number of consecutive grants given to PCI requestor 2

before rotating to the next requestor. This is only valid if there is a non-zero value for the

Request Hold-Grant2 control (H2, bits [43:40]). This may be overidden by either COV,

OV1, or OV0 (bits [23,21,20]. It is also ignored if the ARB.PRE2 bit is cleared.

55:52 R1 Request Repeat 1. Controls the number of consecutive grants given to PCI requestor 1

before rotating to the next requestor. This is only valid if there is a non-zero value for the

Request Hold-Grant1 control (H1, bits [39:36]). This may be overidden by either COV,

OV2, or OV1 (bits [23,22,21]. It is also ignored if the PRE1 (bit 9) is cleared.

51:48 R0 Request Repeat 0. Controls the number of consecutive grants given to PCI requestor 0

before rotating to the next requestor. This is only valid if there is a non-zero value for the

Request Hold-Grant0 control (H0, bits [35:32]). This may be overidden by either the

ARB.COV, ARB.OV2 or ARB.OV1 controls. It is also ignored if PRE0 (bit 8) is cleared.

47:44 CH CPU Hold-Grant Controls. Controls the number of PCI clock edges that the PCI bus

must be idle after a CPU transaction before arbitration continues. This is only valid if

there is a non-zero value for the CPU Repeat field (CR, bits [63:60]). This may be overid-

den by either OV2, OV1, or OV0 (bits [22,21,20]). It is also ignored if CPRE (bit 11) is

cleared.

43:40 H2 Request Hold-Grant 2. Controls the number of PCI clock edges that the PCI bus must

be idle after a requestor 2 transaction before arbitration continues. This is only valid if

there is a non-zero value for the Request Repeat 2 field (R2, bits [59:56]). This may be

overidden by either COV, OV1, or OV0 (bits [23,21,20]). It is also ignored if PRE2 (bit 10)

is cleared.

39:36 H1 Request Hold-Grant 1. Controls the number of PCI clock edges that the PCI bus must

be idle after a requestor 1 transaction before arbitration continues. This is only valid if

there is a non-zero value for the Request Repeat 1 field (R1, bits [55:52]). This may be

overidden by either COV, OV1, or OV0 (bits [23,21,20]). It is also ignored if the if PRE2

(bit 10) is cleared.

35:32 H0 Request Hold-Grant 0. Controls the number of PCI clock ticks that the PCI bus must be

idle after a requestor 0 transaction before arbitration continues. This is only valid if there

is a non-zero value for the Request Repeat 0 field (R0, bits [51:48]). This may be overid-

den by either COV, OV1, or OV0 (bits [23,21,20]). It is also ignored if PRE2 (bit 10) is

cleared.

31:24 RSVD (RO) Reserved (Read Only). Reserved for future use.

23 COV CPU Override. Enables the CPU to override the repeat-count and grant-hold for other

requestors. When COV is set and the CPU is requesting access to PCI, repeat-count and

grant-hold mechanisms for other masters are temporarily disabled. This bit does not

change the round robin arbitration cycle, it only overrides repeat-count and grant-hold for

other requestors.

22 OV2 Override 2. Enables requester2 to override the repeat-count and grant-hold for other

requestors. When OV2 is set and REQ2# is asserted, repeat-count and grant-hold mech-

anisms for other masters are temporarily disabled. This bit does not change the round

robin arbitration cycle, it only overrides repeat-count and grant-hold for other requestors.

21 OV1 Override 1. Enables requester1 to override the repeat-count and grant-hold for other

requestors. When OV1 is set and REQ1# is asserted, repeat-count and grant-hold mech-

anisms for other masters are temporarily disabled. This bit does not change the round

robin arbitration cycle, it only overrides repeat-count and grant-hold for other requestors.