408 AMD Geode™ LX Processors Data Book

Video Processor

33234H

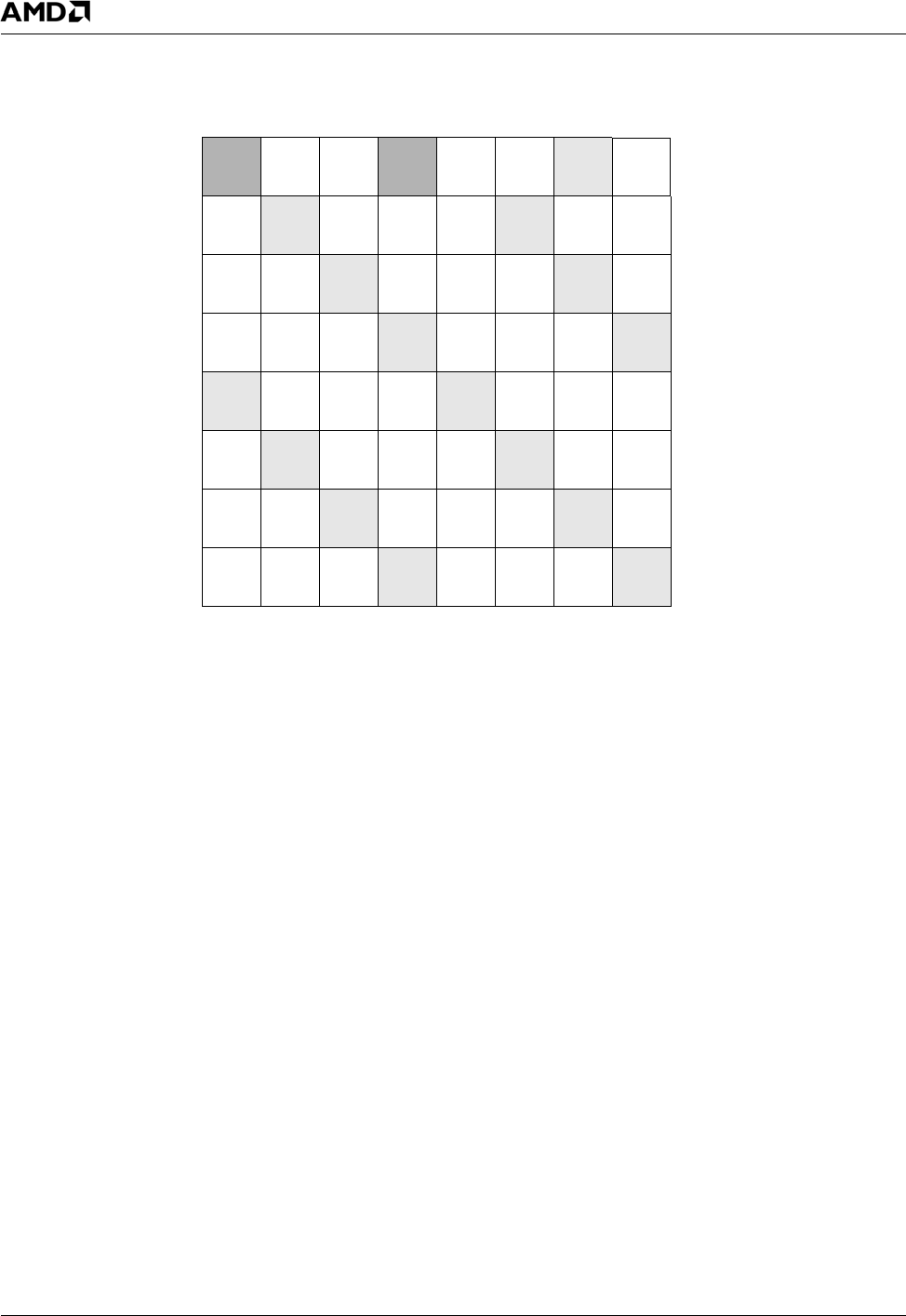

Figure 6-37. Dithered 8x8 Pixel Pattern

All discussions to this point have referred to a 6-bit dither-

ing scheme. A 6-bit dithering scheme is one in which the

least significant six bits of the input intensity value for each

pixel color component are truncated and these least signifi-

cant six bits are used to select an 8x8 dithering pattern.

The FP also supports 4-, 3-, 2-, and 1-bit dithering

schemes. In the 4-bit dithering scheme, only the least sig-

nificant four bits of the input intensity value for each color

component are truncated. As the value of the least signifi-

cant four bits increases from 0 to 15, the order in which 1s

are added to the dithering is much the same as in a 6-bit

scheme except that two 1s are added to the pattern for

each increment of the 4-bit value.

The 3-bit dithering scheme selects a dithering pattern

based on the least significant three bits of the input inten-

sity value for each color component. The order in which 1s

are added to the dithering pattern as the value of these two

bits increases from 0 to 7 is the same as the order for the

6-bit scheme except that two 1s are added to the pattern

for each increment of the 3-bit value.

The 2-bit dithering scheme selects a dithering pattern

based on the least significant two bits of the input intensity

value for each color component. The order in which 1s are

added to the dithering pattern as the value of these two bits

increases from 0 to 3 is the same as the order for the 6-bit

scheme except that four 1s are added to the pattern for

each increment of the 2-bit value.

The 1-bit dithering scheme uses the least significant bit of

the input intensity value to select one of two dithering pat-

terns. The order that 1s are added to the dithering pattern

is the same as the 6-bit scheme except that eight 1s are

added to the pattern when the least significant bit is a 1.

When the least significant bit is 0, the pattern is all 0s.

When the least significant bit is 1, the pattern is alternating

0s and 1s.

Figure 6-38 on page 409 shows the suggested order for

adding 1s to the dithering patterns for the 4-, 3-, 2-, and 1-

bit dithering schemes.

X-Count[3:0]

Y-Count[3:0]

10000000

10000000

01000000

01000000

01000000

01000000

10000000

0100000001000000

01000000

01000000

01000000

10000000

10000000

01000000

01000000

000 001 010 011 100 101 110 111

000

001

010

011

100

101

110

111

10000000

10000000

01000000

01000000

01000000

01000000

01000000

0100000001000000

01000000

01000000

01000000

10000000

10000000

01000000

01000000

01000000

10000000

01000000

01000000

01000000 01000000

01000000

01000000

01000000

10000000

10000000

10000000

01000000

01000000

10000000

10000000

01000000

01000000

01000000

01000000

0100000001000000

01000000

01000000

10000000

10000000

01000000

01000000

0100000001000000

01000000

01000000