AMD Geode™ LX Processors Data Book 257

Graphics Processor Register Definitions

33234H

6.4.1.3 GLD SMI MSR (GLD_MSR_SMI)

This MSR contains the SMI and Mask bits for the GP. An SMI is asserted whenever an illegal address or an illegal type is

detected on the GLIU and the mask bit is not set. This also causes the mb_p_asmi output to be asserted. This signal

remains asserted until the SMI is cleared or the mask bit is set. An illegal address is defined as a memory mapped access

to an address offset greater than 07Fh or an MSR access to an address greater than 20000007h. An illegal type is flagged

if the GP receives a transaction whose type is not one of the following: NCOH_READ, NCOH_WRITE, NCOH_READ_BEX,

MSR_READ, MSR_WRITE, BEX, NULL.

6.4.1.4 GLD Error MSR (GLD_MSR_ERROR)

This MSR contains the Errors and Mask bits for the GP. An error is asserted whenever an illegal address or an illegal type

is detected on the GLIU and the mask bit is not set. This also causes the internal mb_p_asmi output to be asserted if the

Mask bit (MSR A0002002h[0]) is not set. The error bits remain asserted until they are cleared. An illegal address is defined

as a memory mapped access to an address offset greater than 07Fh or an MSR access to an address greater than

20000007h. An illegal type is flagged if the GP receives a transaction whose type is not one of the following: NCOH_READ,

NCOH_WRITE, NCOH_READ_BEX, MSR_READ, MSR_WRITE, BEX, NULL.

MSR Address A0002002h

Typ e R /W

Reset Value 00000000_00000000h

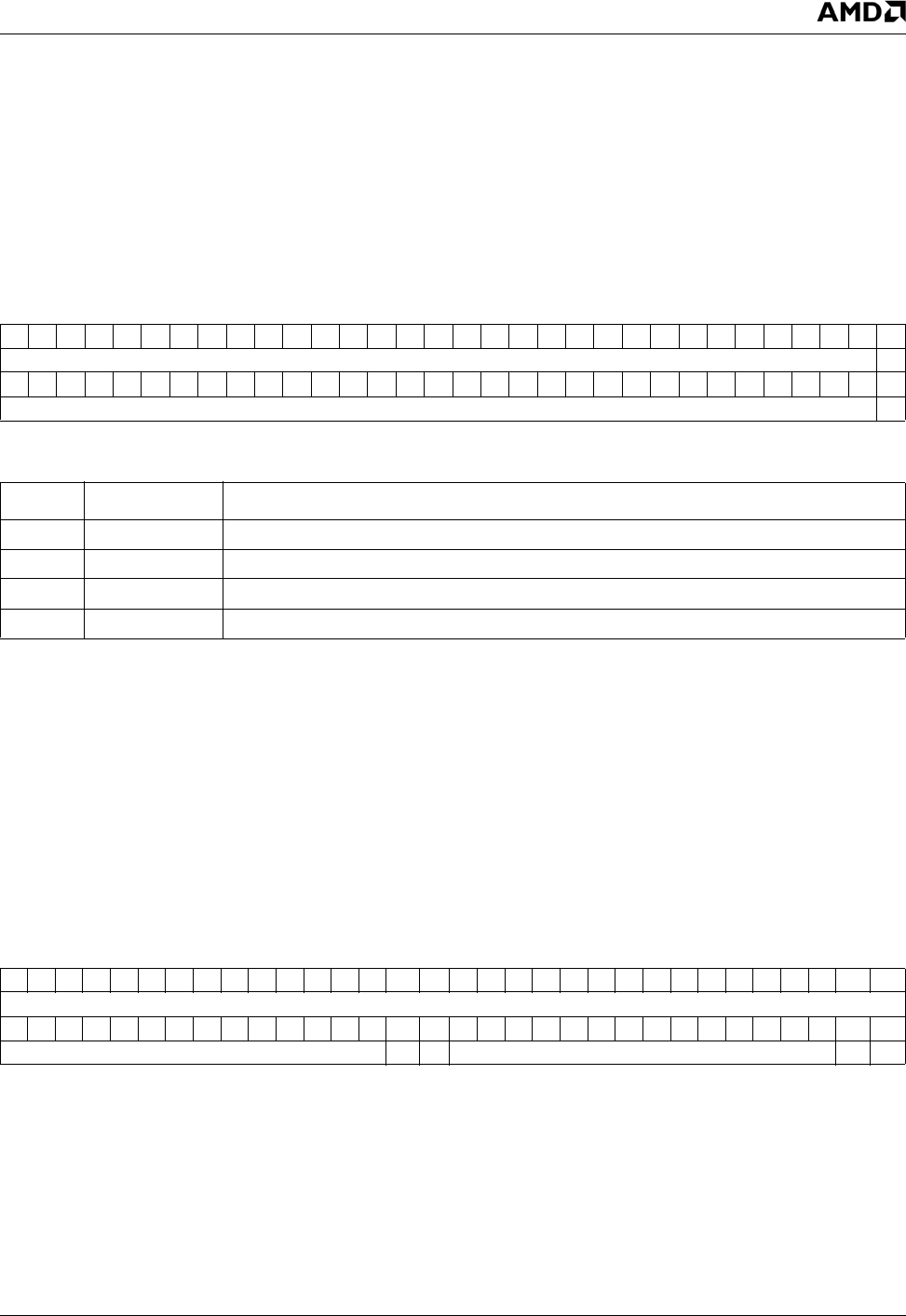

GLD_MSR_SMI Register Map

63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32

RSVD

S

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

RSVD M

GLD_MSR_SMI Bit Descriptions

Bit Name Description

63:33 RSVD Reserved. Read returns 0.

32 S SMI. Indicates address or type violation. Write = 1 clears bit, write = 0 has no effect.

31:1 RSVD Reserved. Read returns 0.

0M Mask. Ignore address and type violations when set; also disable ASMI output.

MSR Address A0002003h

Typ e R /W

Reset Value 00000000_00000000h

GLD_MSR_ERROR Register Map

63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32

RSVD

3130292827262524232221201918171615141312111098765432 1 0

RSVD AE TE RSVD AM TM