AMD Geode™ LX Processors Data Book 187

CPU Core Register Descriptions

33234H

5.5.2.95 L2 Cache Configuration MSR (L2_CONFIG_MSR)

L2_CONFIG_MSR controls the behavior of the L2 cache.

MSR Address 00001920h

Typ e R /W

Reset Value 00000000_0000000Eh

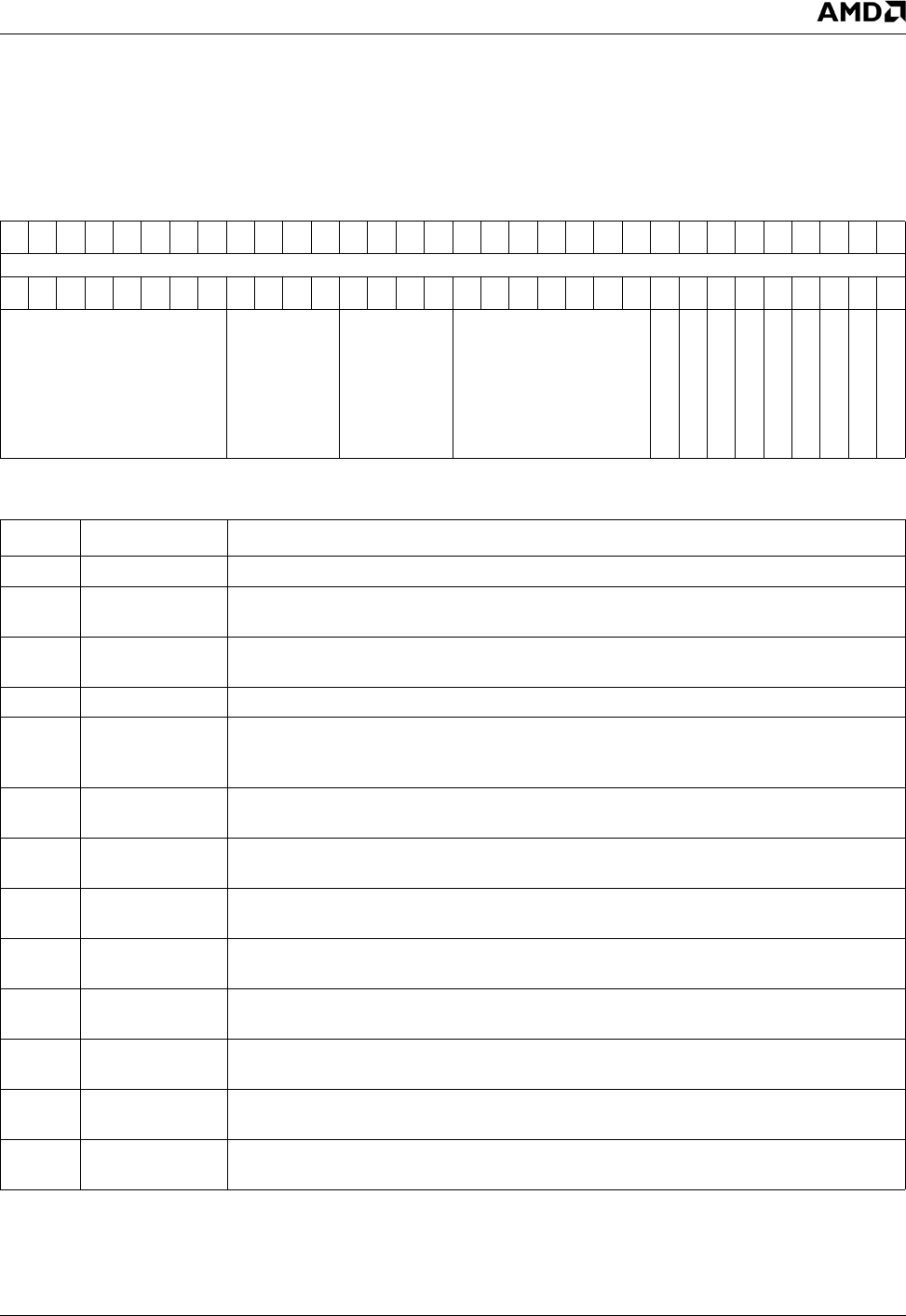

L2_CONFIG_MSR Register Map

63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32

RSVD

313029282726252423222120191817161514131211109876543210

RSVD L2_IM_LOCK L2_DM_LOCK RSVD

L2_TAG_CLKGT_EN

L2_PASS_IOMSR

L2_DMEVCT_DIRTY

L2_WAIT_DM_WR

L2_INVALID

L2_IM_ALLOC_EN

L2_DM_ALLOC_EN

L2_ALLOC_EN

L2_EN

L2_CONFIG_MSR Bit Descriptions

Bit Name Description

63:24 RSVD Reserved.

23:20 L2_IM_LOCK L2 Instruction Memory Subsystem Lock. On allocations from the IM, avoid using the

ways that have the corresponding bits set to 1. (Default = 0)

19:16 L2_DM_LOCK L2 Cache Data Memory Subsystem Lock. On allocations from the DM, avoid using the

ways that have the corresponding bits set to 1. (Default = 0)

15:9 RSVD Reserved.

8 L2_TAG_

CLKGT_EN

L2 Cache Tag Clock Gating Enable. If set, the L2 tags would be clocked only when

accessed. Otherwise, the tags would be clocked whenever the bus controller clocks are

active. (Default = 0)

7 L2_PASS_

IOMSR

L2 Cache (always) Pass I/Os and MSRs. Reserved for Debug only. Pass I/Os and

MSRs through regardless of the state of the L2. (Default = 0)

6 L2_DMEVCT_

DIRTY

L2 Cache Data Memory Subsystem Evictions (always) Dirty. Reserved for Debug

only. Treats all DM evictions as dirty. (Default = 0)

5 L2_WAIT_DM_

WR

L2 Cache Wait for Data Memory Subsystem Writes. Reserved for debug only. Waits

for all data beats from DM before proceeding. (Default = 0)

4 L2_INVALID L2 Cache Invalidate. Invalidate the entire contents of the L2 cache. This bit always

reads back as 0. (Default = 0)

3 L2_IM_ALLOC_

EN

L2 Cache Instruction Memory Subsystem Allocation Enable. A new IM access is

allocated into the L2 cache only if this bit is on. (Default = 1)

2 L2_DM_ALLOC

_EN

L2 Cache Data Memory Subsystem Allocation Enable. A new DM access is allocated

into the L2 cache only if this bit is on. (Default = 1)

1 L2_ALLOC_EN L2 Cache Allocation Enable. A new line is allocated into the L2 cache only if this bit is

on (Default = 1)

0 L2_EN L2 Cache Enable. If this bit is on, the arbiter redirects memory accesses to the L2 block.

(Default = 0)