256 AMD Geode™ LX Processors Data Book

Graphics Processor Register Definitions

33234H

6.4.1 Standard GeodeLink™ Device (GLD) MSRs

6.4.1.1 GLD Capabilities MSR (GLD_MSR_CAP)

This MSR contains the revision and device IDs for the particular implementation of the Graphics Processor. This register is

read only.

6.4.1.2 GLD Master Configuration MSR (GLD_MSR_CONFIG)

This MSR contains the GLIU priority domain bits and priority level bits that are sent out to the GLIU on every GeodeLink

transaction.

MSR Address A0002000h

Typ e RO

Reset Value 00000000_0003D4xxh

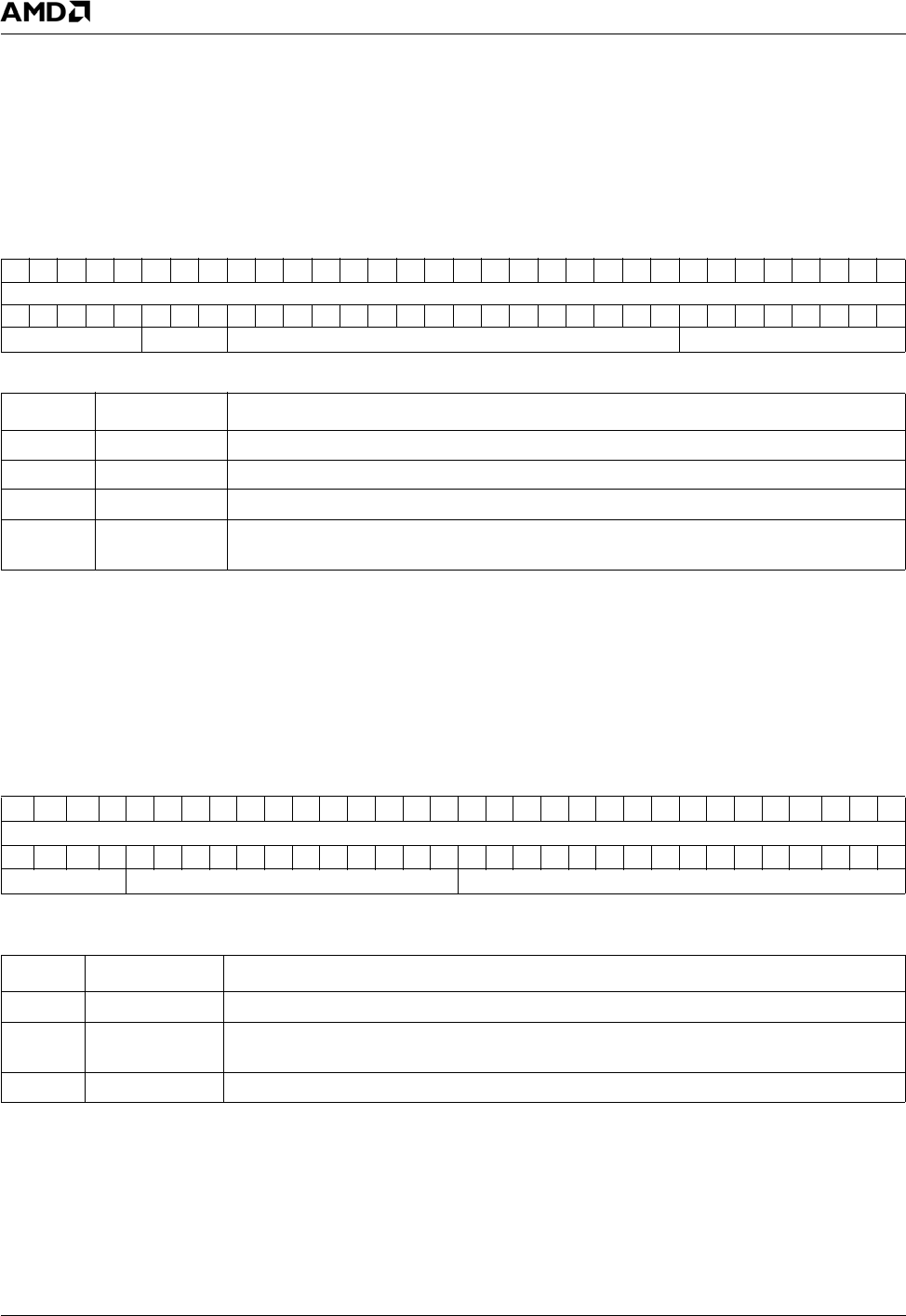

GLD_MSR_CAP Register Map

63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32

RSVD

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

RSVD CLKDOM DID RID

GLD_MSR_CAP Bit Descriptions

Bit Name Description

63:27 RSVD Reserved.

26:24 CLKDOM Clock Domain. Number of clock domains. The GP has one clock domain.

23:8 DID Device ID. Identifies device (03D4h).

7:0 RID Revision ID. Identifies device revision. See AMD Geode™ LX Processors Specification

Update document for value.

MSR Address A0002001h

Typ e R /W

Reset Value 00000000_00000000h

GLD_MSR_CONFIG Register Map

63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32

RSVD

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

RSVD CBASE RSVD

GLD_MSR_CONFIG Bit Descriptions

Bit Name Description

63:28 RSVD Reserved.

27:16 CBASE Command Buffer Base. 16M region aligned to 1M boundary. See Section 6.3.1 "Com-

mand Buffer" on page 239 for details.

15:0 RSVD Reserved.