www.ti.com

7.4.1EDMA3Device-SpecificInformation

7.4.2EDMA3ChannelSynchronizationEvents

SM320C6455-EP

FIXED-POINTDIGITALSIGNALPROCESSOR

SPRS462B–SEPTEMBER2007–REVISEDJANUARY2008

TheEDMAsupportstwoaddressingmodes:constantaddressingandincrementaddressingmode.

Constantaddressingmodeisapplicabletoaverylimitedsetofusecases;formostapplicationsincrement

modecanbeused.OntheC6455DSP,theEDMAcanuseconstantaddressingmodeonlywiththe

EnhancedViterbi-DecoderCoprocessor(VCP2)andtheEnhancedTurboDecoderCoprocessor(TCP2).

ConstantaddressingmodeisnotsupportedbyanyotherperipheralorinternalmemoryintheC6455DSP.

NotethatincrementmodeissupportedbyallC6455peripherals,includingVCP2andTCP2.Formore

informationonthesetwoaddressingmodes,seetheTMS320C645xDSPEnhancedDMA(EDMA3)

ControllerUser'sGuide(literaturenumberSPRU966).

ADSPinterruptmustbegeneratedattheendofanHPIorPCIbootoperationtobeginexecutionofthe

loadedapplication.SincetheDSPinterruptgeneratedbytheHPIandPCIismappedtotheEDMAevent

DSP_EVT(DMAchannel0),itwillgetrecordedinbit0oftheEDMAEventRegister(ER).Thiseventmust

beclearedbysoftwarebeforetriggeringtransfersonDMAchannel0.TheEDMA3ontheC6455DSP

supportsactivememoryprotection,butitdoesnotsupportproxiedmemoryprotection.

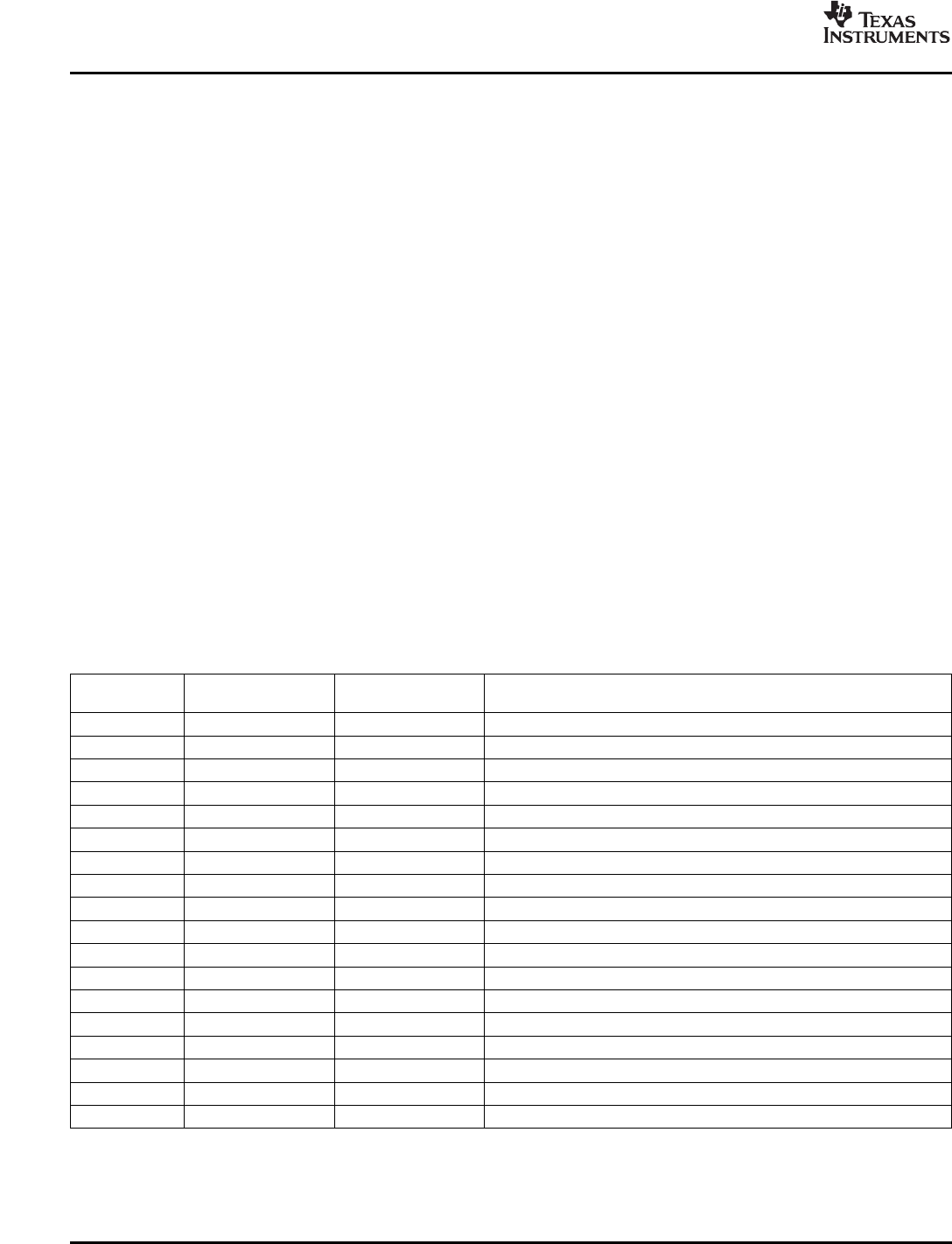

TheEDMA3supportsupto64DMAchannelsthatcanbeusedtoservicesystemperipheralsandtomove

databetweensystemmemories.DMAchannelscanbetriggeredbysynchronizationeventsgeneratedby

systemperipherals.Table7-3liststhesourceofthesynchronizationeventassociatedwitheachofthe

DMAchannels.OntheC6455,theassociationofeachsynchronizationeventandDMAchannelisfixed

andcannotbereprogrammed.

FormoredetailedinformationontheEDMA3moduleandhowEDMA3eventsareenabled,captured,

processed,prioritized,linked,chained,andcleared,etc.,seetheTMS320C645xDSPEnhancedDMA

(EDMA3)ControllerUser'sGuide(literaturenumberSPRU966).

Table7-3.C6455EDMA3ChannelSynchronizationEvents

(1)

EDMA

BINARYEVENTNAMEEVENTDESCRIPTION

CHANNEL

0

(2)

0000000DSP_EVTHPI/PCI-to-DSPevent

10000001TEVTLO0Timer0lowercounterevent

20000010TEVTHI0Timer0highcounterevent

30000011-None

40000100-None

50000101-None

60000110-None

70000111-None

80001000-None

90001001-None

100001010-None

110001011-None

120001100XEVT0McBSP0transmitevent

130001101REVT0McBSP0receiveevent

140001110XEVT1McBSP1transmitevent

150001111REVT1McBSP1receiveevent

160010000TEVTLO1Timer1lowercounterevent

170010001TEVTHI1Timer1highcounterevent

(1)Inadditiontotheeventsshowninthistable,eachofthe64channelsalsocanbesynchronizedwiththetransfercompletionoralternate

transfercompletionevents.FormoredetailedinformationonEDMAevent-transferchaining,seetheTMS320C645xDSPEnhanced

DMA(EDMA3)ControllerUser'sGuide(literaturenumberSPRU966).

(2)HPIbootandPCIbootareterminatedusingaDSPinterrupt.TheDSPinterruptisregisteredinbit0(channel0)oftheEDMAEvent

Register(ER).ThiseventmustbeclearedbysoftwarebeforetriggeringtransfersonDMAchannel0.

C64x+PeripheralInformationandElectricalSpecifications 110SubmitDocumentationFeedback