www.ti.com

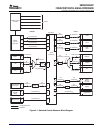

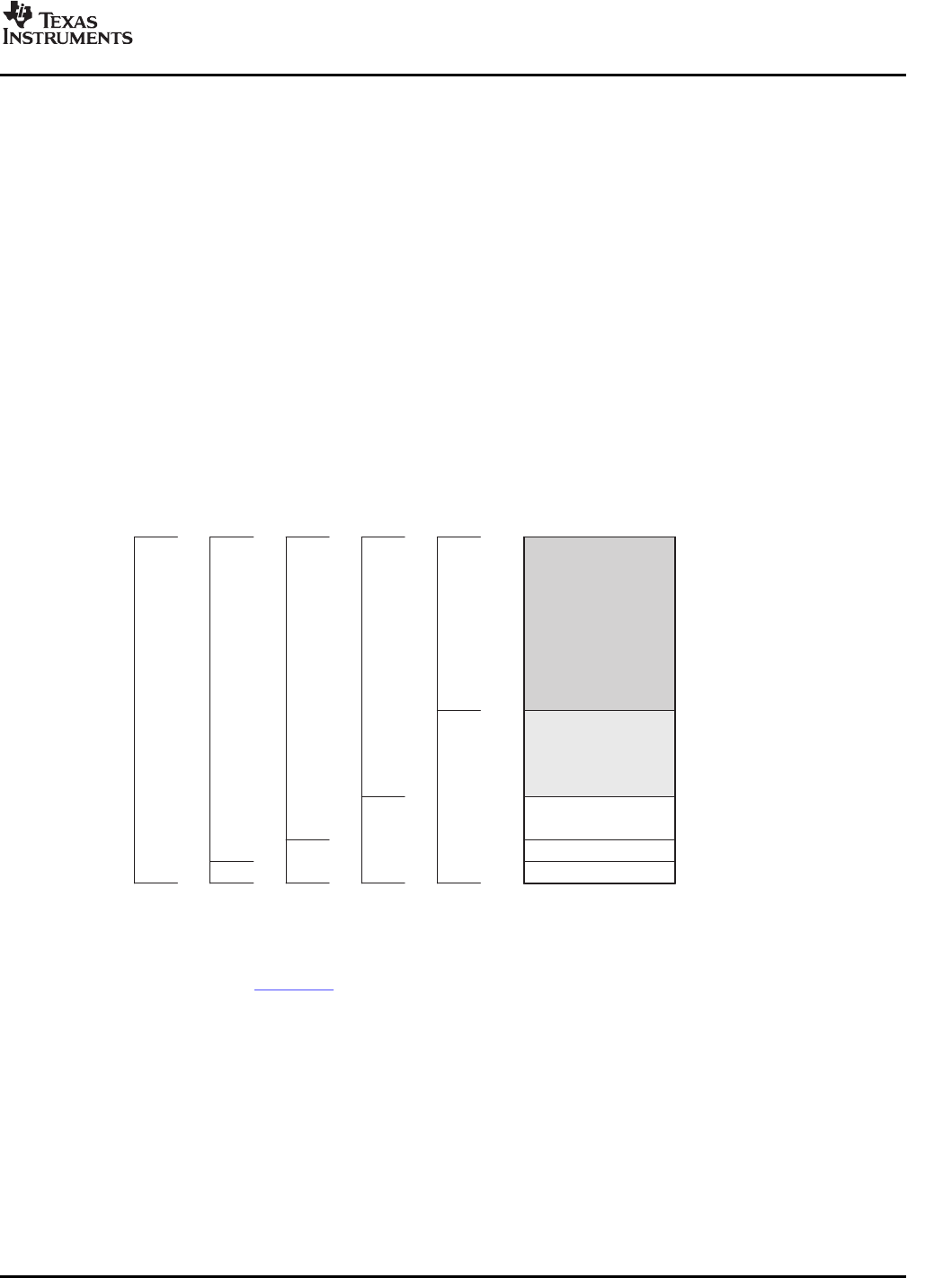

32K bytes

32K bytes

64K bytes

128K bytes

1840K bytes

L2 memory

0080 0000h

009C 0000h

009E 0000h

009F 0000h

009F 8000h

00A0 0000h

7/8

SRAM

4-way

cache

4-way

cache

SRAM

15/16

4-way

31/32

SRAM

4-way

SRAM

63/64

All

SRAM

000 001 010 011 111

Block base

address

L2 mode bits

cache

SM320C6455-EP

FIXED-POINTDIGITALSIGNALPROCESSOR

SPRS462B–SEPTEMBER2007–REVISEDJANUARY2008

TheL2memoryconfigurationfortheC6455deviceisasfollows:

•Port0configuration:

–Memorysizeis2096KB

–Startingaddressis00800000h

–2-cyclelatency

–4×128bitbankconfiguration

•Port1configuration:

–Memorysizeis32Kbytes(thiscorrespondstotheinternalROM)

–Startingaddressis00100000h

–1-cyclelatency

–1×256bitbankconfiguration

L2memorycanbeconfiguredasallSRAMoraspart4-wayset-associativecache.TheamountofL2

memorythatisconfiguredascacheiscontrolledthroughtheL2MODEfieldoftheL2Configuration

Register(L2CFG)oftheC64x+Megamodule.Figure5-4showstheavailableSRAM/cacheconfigurations

forL2.Bydefault,L2isconfiguredasallSRAMafterdevicereset.

Figure5-4.C6455L2MemoryConfigurations

FormoreinformationontheoperationL1andL2caches,seetheTMS320C64x+DSPCacheUser's

Guide(literaturenumberSPRU862).

AllmemoryontheC6455hasauniquelocationinthememorymap(seeTable2-2,C6455MemoryMap

Summary).

WhenaccessingtheinternalROMoftheDSP,theCPUfrequencymustbelessthan750MHz.Therefore,

whenusingasoftwarebootmode,caremustbetakensuchthattheCPUfrequencydoesnotexceed750

MHzatanypointduringthebootsequence.Afterthebootsequencehascompleted,theCPUfrequency

canbeprogrammedtothefrequencyrequiredbytheapplication.Formoredetailedinformationonthe

bootmodes,seeSection2.4,BootSequence.

SubmitDocumentationFeedbackC64x+Megamodule89