www.ti.com

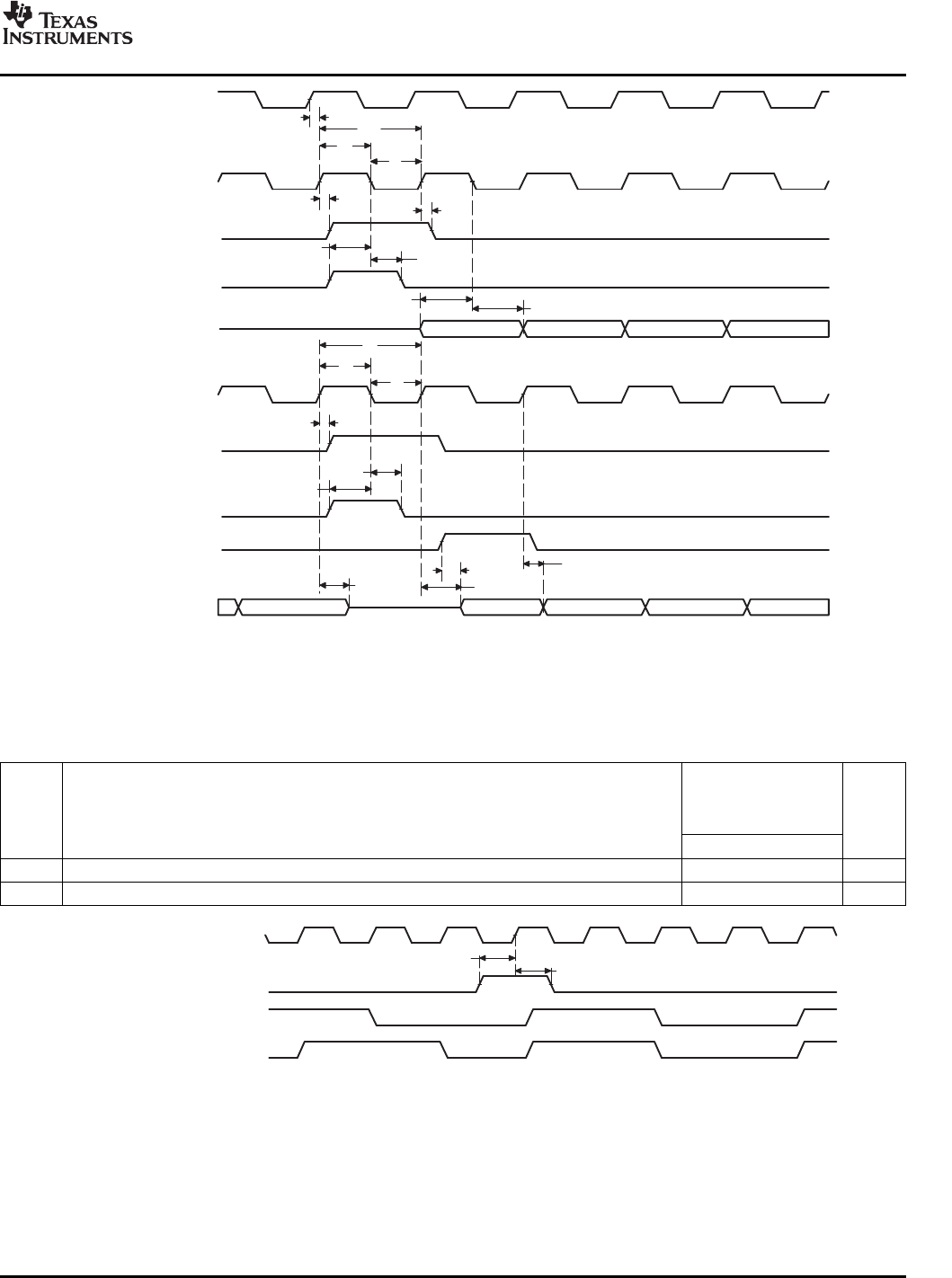

Bit(n-1) (n-2) (n-3)

Bit 0 Bit(n-1) (n-2) (n-3)

14

12

11

10

9

3

3

2

8

7

6

5

4

4

3

1

3

2

CLKS

CLKR

FSR (int)

FSR (ext)

DR

CLKX

FSX (int)

FSX (ext)

FSX (XDATDLY=00b)

DX

13

(A)

13

(A)

2

1

CLKS

FSR external

CLKR/X (no need to resync)

CLKR/X (needs resync)

SM320C6455-EP

FIXED-POINTDIGITALSIGNALPROCESSOR

SPRS462B–SEPTEMBER2007–REVISEDJANUARY2008

A.ParameterNo.13appliestothefirstdatabitonlywhenXDATDLY≠0.

B.TheCLKSsignalissharedbybothMcBSP0andMcBSP1onthisdevice.

Figure7-52.McBSPTiming

(B)

Table7-61.TimingRequirementsforFSRWhenGSYNC=1(seeFigure7-53)

-720

-850

A-1000/-1000

NO.UNIT

-1200

MINMAX

1t

su(FRH-CKSH)

Setuptime,FSRhighbeforeCLKShigh4ns

2t

h(CKSH-FRH)

Holdtime,FSRhighafterCLKShigh4ns

Figure7-53.FSRTimingWhenGSYNC=1

SubmitDocumentationFeedbackC64x+PeripheralInformationandElectricalSpecifications195