www.ti.com

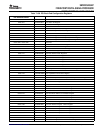

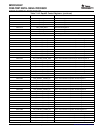

P47 P48 H1

N 0x1F N 0x1F N + 1 0x1F

N N

10

8

4

3

2

1

UXCLK

UXDATA[7:0]

UXADDR[4:0]

UXCLAV

UXENB

UXSOC

9

P46P45

0 x1F

A. The UTOPIA Slave module has signals that are middle-level signals indicating a high-impedance state (i.e., the UXCLAV and UXSOC signals).

5

6

7

SM320C6455-EP

FIXED-POINTDIGITALSIGNALPROCESSOR

SPRS462B–SEPTEMBER2007–REVISEDJANUARY2008

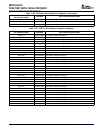

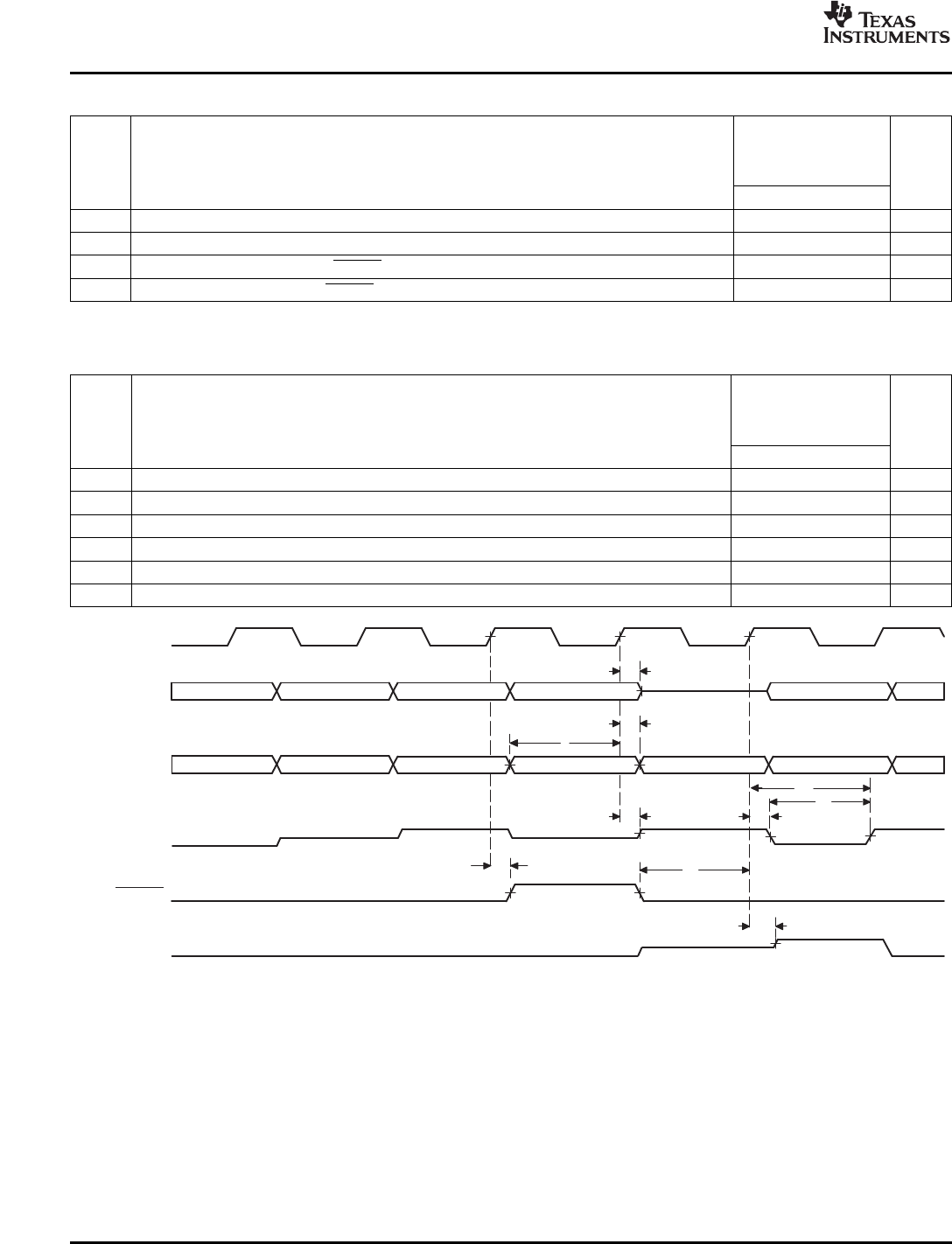

Table7-108.TimingRequirementsforUTOPIASlaveTransmit(seeFigure7-76)

-720

-850

A-1000/-1000

NO.UNIT

-1200

MINMAX

2t

su(UXAV-UXCH)

Setuptime,UXADDRvalidbeforeUXCLKhigh4ns

3t

h(UXCH-UXAV)

Holdtime,UXADDRvalidafterUXCLKhigh1ns

8t

su(UXENBL-UXCH)

Setuptime,UXENBlowbeforeUXCLKhigh4ns

9t

h(UXCH-UXENBL)

Holdtime,UXENBlowafterUXCLKhigh1ns

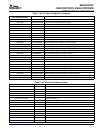

Table7-109.SwitchingCharacteristicsOverRecommendedOperatingConditionsforUTOPIASlave

TransmitCycles(seeFigure7-76)

-720

-850

A-1000/-1000

NO.PARAMETERUNIT

-1200

MINMAX

1t

d(UXCH-UXDV)

Delaytime,UXCLKhightoUXDATAvalid312ns

4t

d(UXCH-UXCLAV)

Delaytime,UXCLKhightoUXCLAVdrivenactivevalue312ns

5t

d(UXCH-UXCLAVL)

Delaytime,UXCLKhightoUXCLAVdriveninactivelow312ns

6t

d(UXCH-UXCLAVHZ)

Delaytime,UXCLKhightoUXCLAVgoingHi-Z918.5ns

7t

w(UXCLAVL-UXCLAVHZ)

Pulseduration(low),UXCLAVlowtoUXCLAVHi-Z3ns

10t

d(UXCH-UXSV)

Delaytime,UXCLKhightoUXSOCvalid312ns

Figure7-76.UTOPIASlaveTransmitTiming

(A)

232C64x+PeripheralInformationandElectricalSpecificationsSubmitDocumentationFeedback