www.ti.com

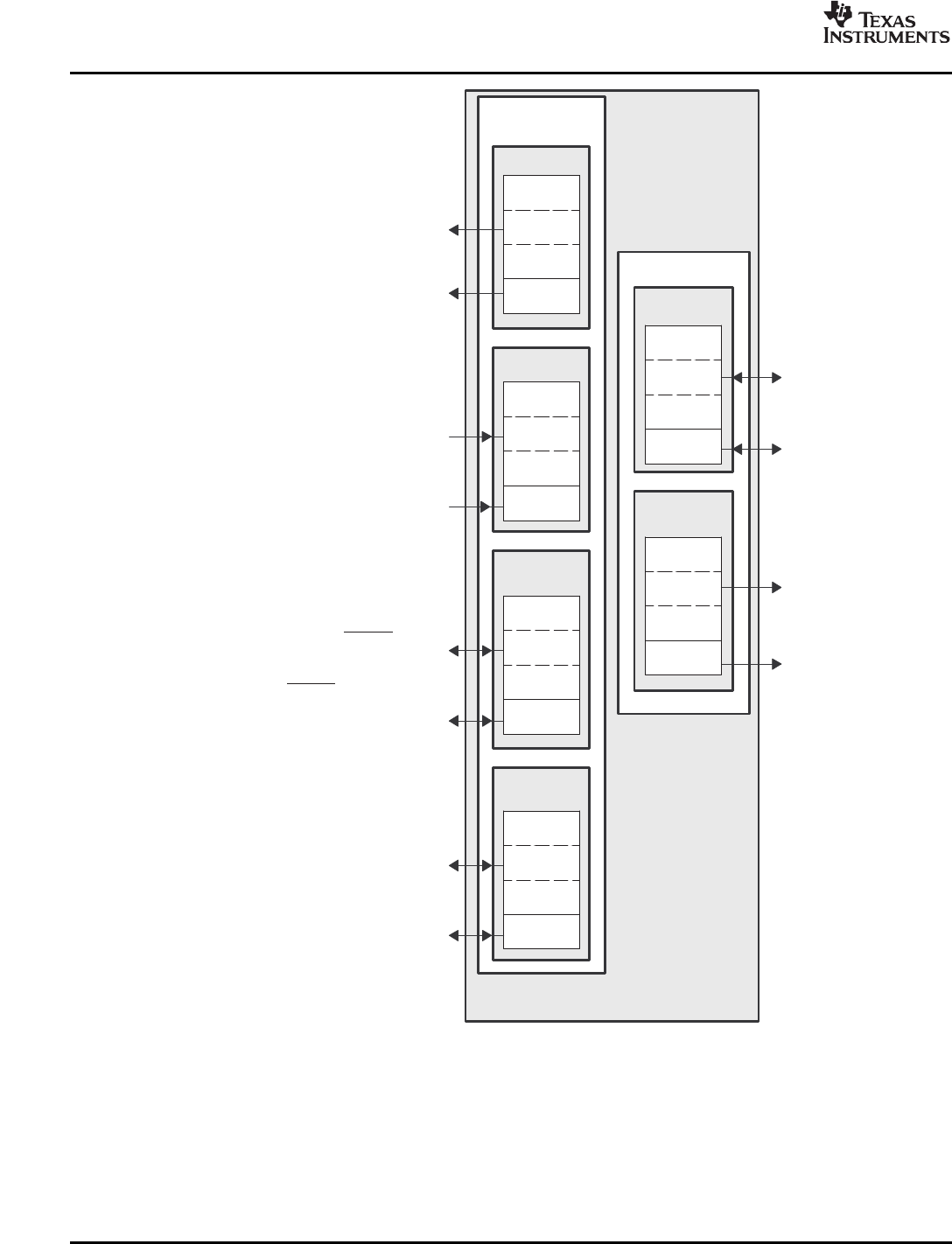

RGTXCTL, RGRXCTL

URSOC/MRXER/RMRXER,

URENB/MRXDV,

URCLAV/MCRS/RMCRSDV,

UXSOC/MCOL,

UXENB/MTXEN/RMTXEN

Ethernet MAC (EMAC) and MDIO

(B)

UXADDR3/MDIO

UXADDR4/MDCLK

MDIO

Clock

Clocks

Error Detect

and Control

Input/Output

Receive

RGMDIO

RGMDCLK

RGTXD[3:0]

A. RGMII signals are mutually exclusive to all other EMAC signals.

B. These EMAC pins are muxed with the UTOPIA peripheral. By default, these signals function as EMAC. For more details on these

muxed pins, see the Device Configuration section of this document.

RGTXC,

RGRXC,

RGREFCLK

UXDATA[7:2]/MTXD[7:2],

UXDATA[1:0]/MTXD[1:0]/RMTXD[1:0]

Transmit

RGMII

(A)

GMII

RMII

MII

RGRXD[3:0]

URDATA[7:2]/MRXD[7:2],

URDATA[1:0]/MRXD[1:0]/RMRXD[1:0]

RGMII

(A)

GMII

RMII

MII

RGMII

(A)

GMII

RMII

MII

RGMII

(A)

GMII

RMII

MII

RGMII

(A)

GMII

RMII

MII

GMII

RMII

MII

RGMII

(A)

UXCLK/MTCLK/RMREFCLK,

URCLK/MRCLK,

UXCLAV/GMTCLK

Ethernet MAC

(EMAC)

SM320C6455-EP

FIXED-POINTDIGITALSIGNALPROCESSOR

SPRS462B–SEPTEMBER2007–REVISEDJANUARY2008

Figure2-10.EMAC/MDIO[MII/RMII/GMII/RGMII]PeripheralSignals

DeviceOverview 28SubmitDocumentationFeedback