www.ti.com

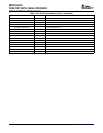

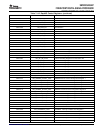

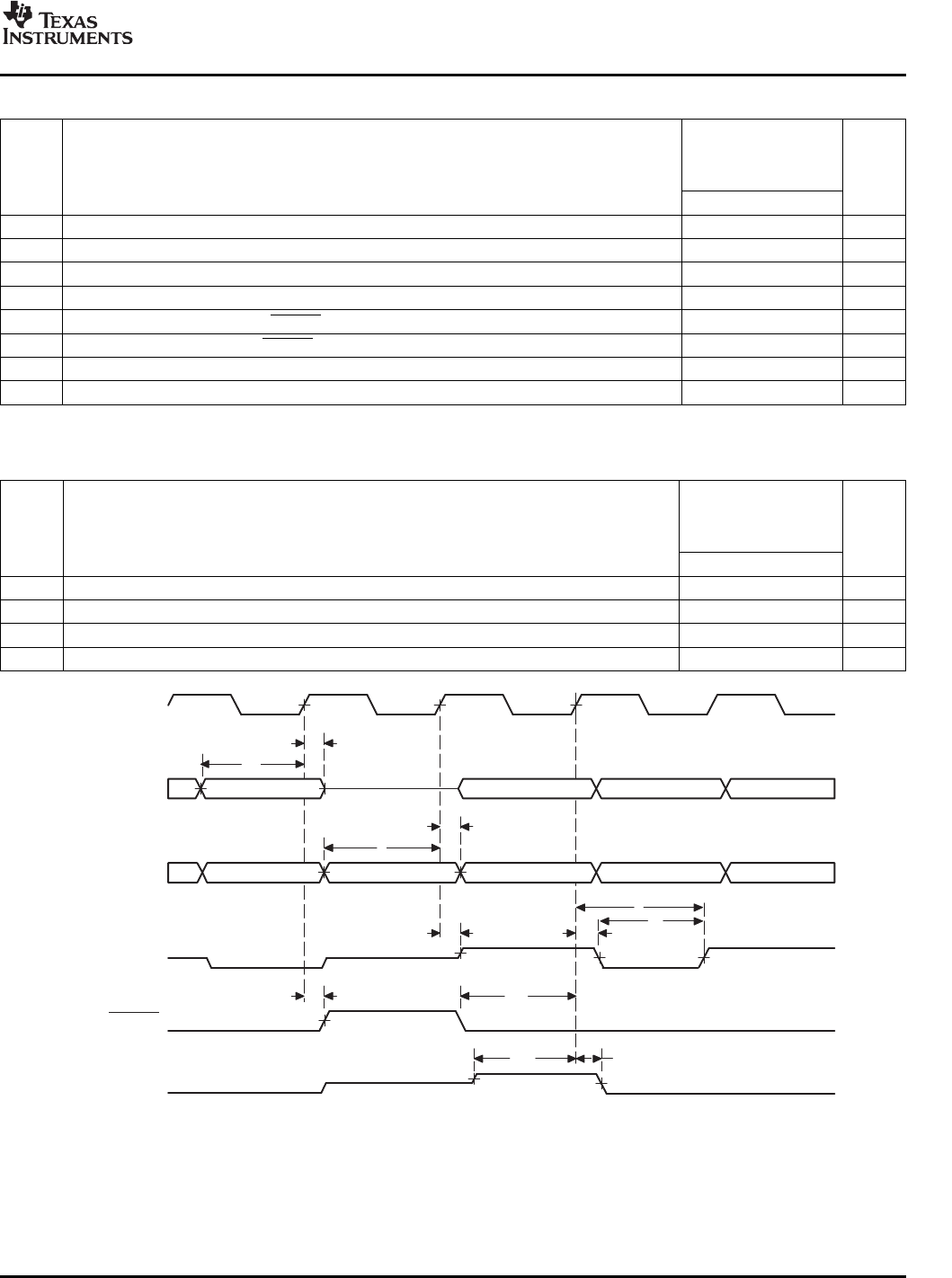

P48 H1 H2 H3

N 0x1F N+1 0x1F N+2 0x1F

N N+1 N+2

1211

9

10

5

4

3

2

1

URCLK

URDATA[7:0]

URADDR[4:0]

URCLAV

URENB

URSOC

A. The UTOPIA Slave module has signals that are middle-level signals indicating a high-impedance state (i.e., the URCLAV and

URSOC signals).

8

6

7

SM320C6455-EP

FIXED-POINTDIGITALSIGNALPROCESSOR

SPRS462B–SEPTEMBER2007–REVISEDJANUARY2008

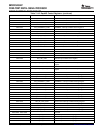

Table7-110.TimingRequirementsforUTOPIASlaveReceive(seeFigure7-77)

-720

-850

A-1000/-1000

NO.UNIT

-1200

MINMAX

1t

su(URDV-URCH)

Setuptime,URDATAvalidbeforeURCLKhigh4ns

2t

h(URCH-URDV)

Holdtime,URADDRvalidafterURCLKhigh1ns

3t

su(URAV-URCH)

Setuptime,URADDRvalidbeforeURCLKhigh4ns

4t

h(URCH-URAV)

Holdtime,URADDRvalidafterURCLKhigh1ns

9t

su(URENBL-URCH)

Setuptime,URENBlowbeforeURCLKhigh4ns

10t

h(URCH-URENBL)

Holdtime,URENBlowafterURCLKhigh1ns

11t

su(URSH-URCH)

Setuptime,URSOChighbeforeURCLKhigh4ns

12t

h(URCH-URSH)

Holdtime,URSOChighafterURCLKhigh1ns

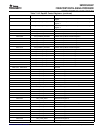

Table7-111.SwitchingCharacteristicsOverRecommendedOperatingConditionsforUTOPIASlave

ReceiveCycles(seeFigure7-77)

-720

-850

A-1000/-1000

NO.PARAMETERUNIT

-1200

MINMAX

5t

d(URCH-URCLAV)

Delaytime,URCLKhightoURCLAVdrivenactivevalue312ns

6t

d(URCH-URCLAVL)

Delaytime,URCLKhightoURCLAVdriveninactivelow312ns

7t

d(URCH-URCLAVHZ)

Delaytime,URCLKhightoURCLAVgoingHi-Z918.5ns

8t

w(URCLAVL-URCLAVHZ)

Pulseduration(low),URCLAVlowtoURCLAVHi-Z3ns

Figure7-77.UTOPIASlaveReceiveTiming

(A)

SubmitDocumentationFeedbackC64x+PeripheralInformationandElectricalSpecifications233