www.ti.com

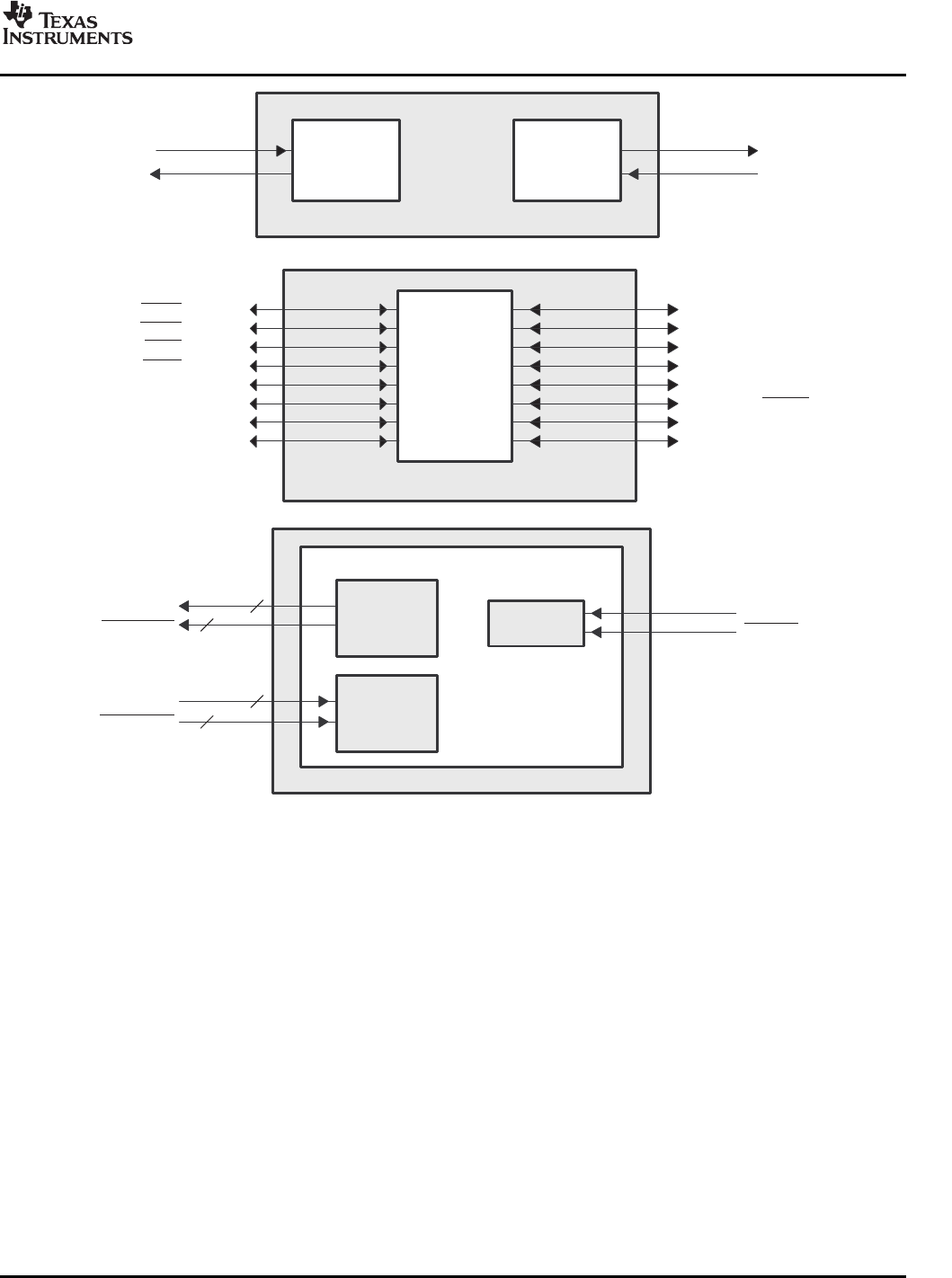

A. This pin functions as GP[1] by default. For more details, see the Device Configuration section of this document.

B. These McBSP1 peripheral pins are muxed with the GPIO peripheral pins and by default these signals function as GPIO peripheral pins. For

more details, see the Device Configuration section of this document.

C. These UTOPIA and PCI peripheral pins are muxed with the GPIO peripheral pins and by default these signals function as GPIO peripheral

pins. For more details, see the Device Configuration section of this document.

GPIO

General-Purpose Input/Output 0 (GPIO) Port

CLKX1/GP[3]

(B)

URADDR4/PCBE0/GP[2]

(C)

SYSCLK4/GP[1]

(A)

URADDR3/PREQ/GP[15]

(C)

URADDR2/PINTA/GP[14]

(C)

URADDR1/PRST/GP[13]

(C)

URADDR0/PGNT/GP[12]

(C)

FSX1/GP[11]

(B)

FSR1/GP[10]

(B)

DX1/GP[9]

(B)

DR1/GP[8]

(B)

GP[7]

GP[6]

GP[5]

GP[4]

CLKR1/GP[0]

(B)

Timers (64-Bit)

TINPL1

Timer 1

Timer 0

TOUTL1

TINPL0

TOUTL0

RIOCLK

Clock

RIOTX[3:0]

RAPID IO

Transmit

Receive

RIOCLK

4

4

4

4

RIOTX[3:0]

RIORX[3:0]

RIORX[3:0]

SM320C6455-EP

FIXED-POINTDIGITALSIGNALPROCESSOR

SPRS462B–SEPTEMBER2007–REVISEDJANUARY2008

Figure2-7.Timers/GPIO/RapidIOPeripheralSignals

SubmitDocumentationFeedbackDeviceOverview25