www.ti.com

7.7.1.2PLL1ControllerOperatingModes

7.7.1.3PLL1Stabilization,Lock,andResetTimes

SM320C6455-EP

FIXED-POINTDIGITALSIGNALPROCESSOR

SPRS462B–SEPTEMBER2007–REVISEDJANUARY2008

•SYSCLK4isusedastheinternalclockfortheEMIFA.Itisalsousedtoclockotherlogicwithinthe

DSP.

•SYSCLK5clockstheemulationandtracelogicoftheDSP.

ThedividerratiobitsofdividersD2andD3arefixedat÷3and÷6,respectively.Thedividerratiobitsof

dividersD4and54areprogrammablethroughthePLLcontrollerdividerregistersPLLDIV4andPLLDIV5,

respectively.

ThePLLmultipliercontroller(PLLM)andthedividers(D4andD5)mustbeprogrammedafterreset.There

isnohardwareCLKMODEselectionontheC6455device.

SincethedividerratiobitsfordividersD2andD3arefixed,thefrequencyofSYSCLK2andSYSCLK3is

tiedtothefrequencyofSYSREFCLK.However,thefrequencyofSYSCLK4andSYSCLK5dependson

theconfigurationofdividersD4andD5.Forexample,withPLLMinthePLL1multiplycontrolregisterset

to10011b(x20mode)anda50MHzCLKIN1input,thePLLoutputPLLOUTissetto1200MHzand

SYSCLK2andSYSCLK3runat333MHzand166MHz,respectively.DividerD4canbeprogrammed

throughthePLLDIV4registertodivideSYSREFCLKby10suchthatSYSCLK4,andhencetheEMIF

internalclock,runsat100MHz.

Allhosts(HPI,PCI,etc.)mustholdoffaccessestotheDSPwhilethefrequencyofitsinternalclocksis

changing.AmechanismmustbeinplacesuchthattheDSPnotifiesthehostwhenthePLLconfiguration

hascompleted.

NotethatthereisaminimumandmaximumoperatingfrequencyforPLLREF,PLLOUT,SYSCLK4,and

SYSCLK5.ThePLL1Controllermustnotbeconfiguredtoexceedanyoftheseconstraints(certain

combinationsofexternalclockinput,internaldividers,andPLLmultiplyratiosmightnotbesupported).For

thePLLclocksinputandoutputfrequencyranges,seeTable7-16.

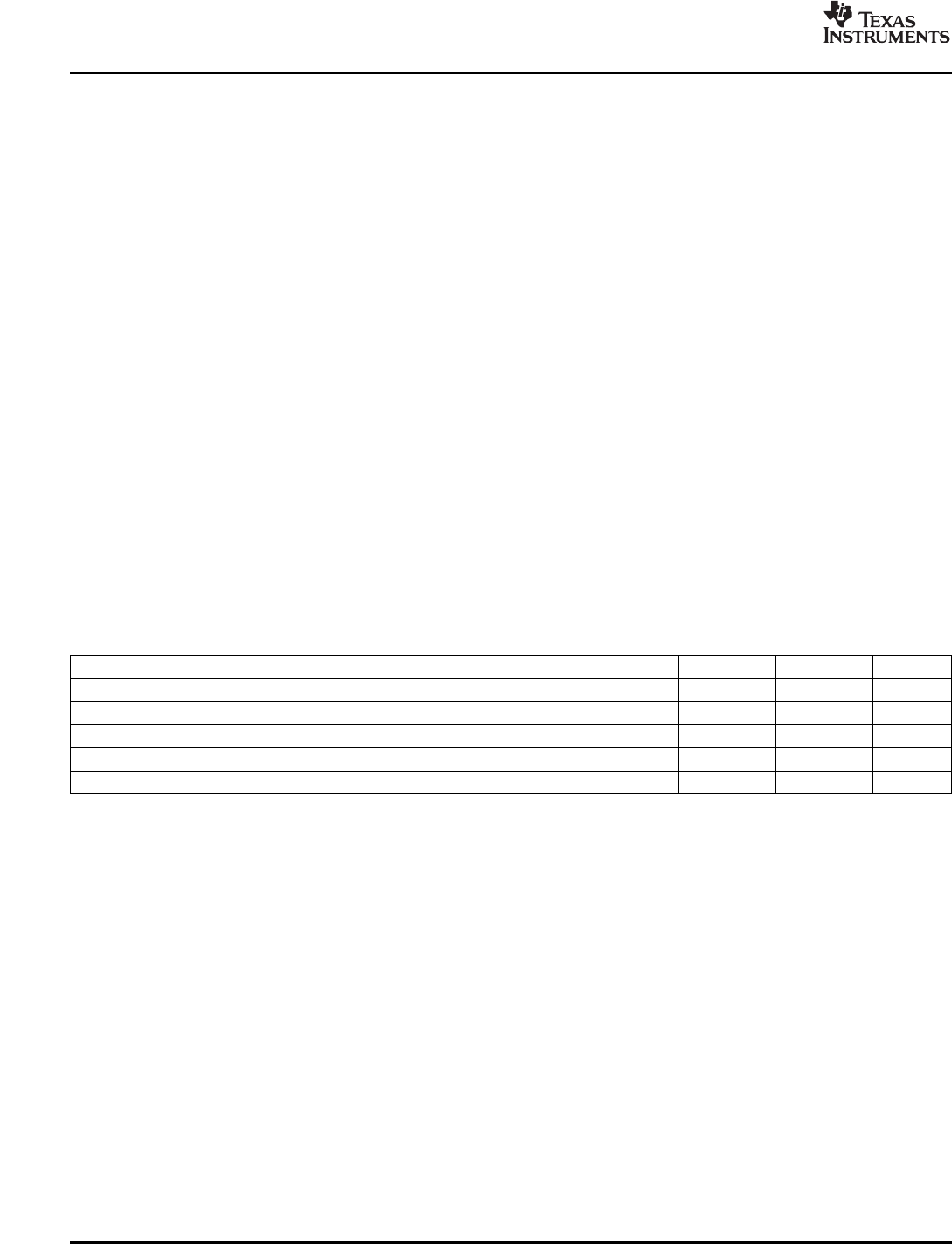

Table7-16.PLL1ClockFrequencyRanges

CLOCKSIGNALMINMAXUNIT

CLKIN166.6MHz

PLLREF(PLLEN=1)

(1)

33.366.6MHz

PLLOUT

(1)

4001200MHz

SYSCLK425166MHz

SYSCLK5333MHz

(1)OnlyapplieswhenthePLL1ControllerissettoPLLmode(PLLEN=1inthePLLCTLregister).

ThePLL1controllerhastwomodesofoperation:bypassmodeandPLLmode.Themodeofoperationis

determinedbythePLLENbitofthePLLcontrolregister(PLLCTL).InPLLmode,SYSREFCLKis

generatedfromthedeviceinputclockCLKIN1usingthedividerPREDIVandthePLLmultiplierPLLM.In

bypassmode,CLKIN1isfeddirectlytoSYSREFCLK.

Allhosts(HPI,PCI,etc.)mustholdoffaccessestotheDSPwhilethefrequencyofitsinternalclocksis

changing.AmechanismmustbeinplacesuchthattheDSPnotifiesthehostwhenthePLLconfiguration

hascompleted.

ThePLLstabilizationtimeistheamountoftimethatmustbeallottedfortheinternalPLLregulatorsto

becomestableafterdevicepowerup.ThePLLshouldnotbeoperateduntilthisstabilizationtimehas

expired.

ThePLLresettimeistheamountofwaittimeneededwhenresettingthePLL(writingPLLRST=1),in

orderforthePLLtoproperlyreset,beforebringingthePLLoutofreset(writingPLLRST=0).Forthe

PLL1resettimevalue,seeTable7-17.

C64x+PeripheralInformationandElectricalSpecifications 138SubmitDocumentationFeedback