www.ti.com

7.8.2PLL2ControllerMemoryMap

7.8.3PLL2ControllerRegisterDescriptions

SM320C6455-EP

FIXED-POINTDIGITALSIGNALPROCESSOR

SPRS462B–SEPTEMBER2007–REVISEDJANUARY2008

ThememorymapofthePLL2controllerisshowninTable7-32.Notethatonlyregistersdocumentedhere

areaccessibleontheC6455.OtheraddressesinthePLL2controllermemorymapshouldnotbe

modified.

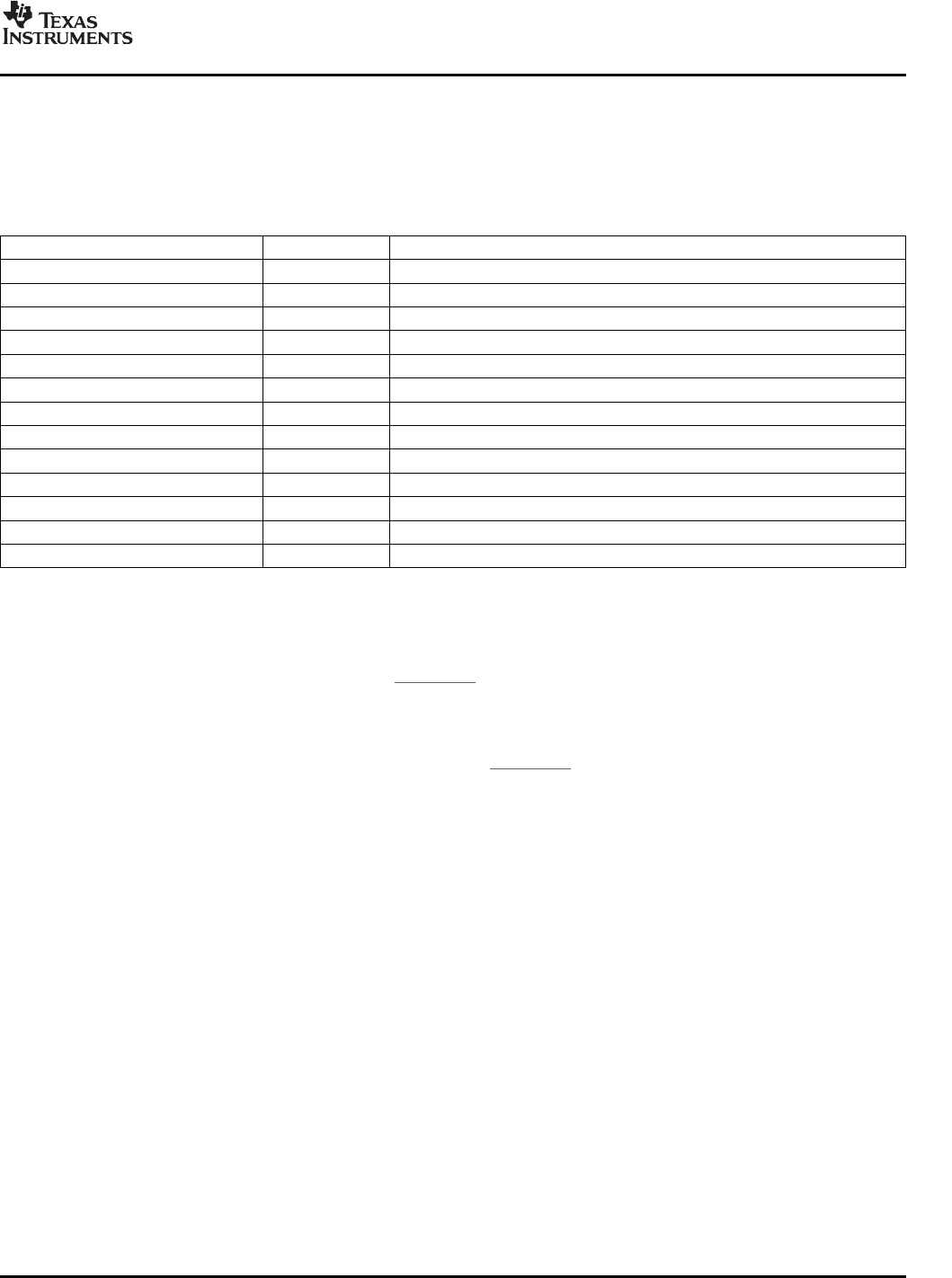

Table7-32.PLL2ControllerRegisters

HEXADDRESSRANGEACRONYMDESCRIPTION

029C0000-029C0114-Reserved

029C0118PLLDIV1PLLControllerDivider1Register

029C011C-029C0134-Reserved

029C0138PLLCMDPLLControllerCommandRegister

029C013CPLLSTATPLLControllerStatusRegister

029C0140ALNCTLPLLControllerClockAlignControlRegister

029C0144DCHANGEPLLDIVRatioChangeStatusRegister

029C0148-Reserved

029C014C-Reserved

029C0150SYSTATSYSCLKStatusRegister

029C0154-029C0190-Reserved

029C0194-029C01FF-Reserved

029C0200-029CFFFF-Reserved

ThissectionprovidesadescriptionofthePLL2controllerregisters.FordetailsontheoperationofthePLL

controllermodule,seetheTMS320C645xDSPSoftware-ProgrammablePhase-LockedLoop(PLL)

ControllerUser'sGuide(literaturenumberSPRUE56).

NOTE:ThePLL2controllerregisterscanonlybeaccessedusingtheCPUortheemulator.

NotalloftheregistersdocumentedintheTMS320C645xDSPSoftware-ProgrammablePhase-Locked

Loop(PLL)ControllerUser'sGuide(literaturenumberSPRUE56)aresupportedontheC6455.Onlythose

registersdocumentedinthissectionaresupported.Furthermore,onlythebitswithintheregisters

describedherearesupported.Youshouldnotwritetoanyreservedmemorylocationorchangethevalue

ofreservedbits.

SubmitDocumentationFeedbackC64x+PeripheralInformationandElectricalSpecifications153