www.ti.com

7.18PeripheralComponentInterconnect(PCI)

7.18.1PCIDevice-SpecificInformation

SM320C6455-EP

FIXED-POINTDIGITALSIGNALPROCESSOR

SPRS462B–SEPTEMBER2007–REVISEDJANUARY2008

TheC6455DSPsupportsconnectionstoaPCIbackplaneviatheintegratedPCImaster/slavebus

interface.ThePCIportinterfacestoDSPinternalresourcesviathedataswitchedcentralresource.The

dataswitchedcentralresourceisdescribedinmoredetailinSection4.

FormoredetailedinformationonthePCIportperipheralmodule,seetheTMS320C645xDSPPeripheral

ComponentInterconnect(PCI)User'sGuide(literaturenumberSPRUE60).

ThePCIperipheralontheC6455DSPconformstothePCILocalBusSpecification(version2.3).ThePCI

peripheralcanactbothasaPCIbusmasterandasatarget.ItsupportsPCIbusoperationofspeedsup

to66MHzandusesa32bitdata/addressbus.

OntheC6455device,thepinsofthePCIperipheralaremultiplexedwiththepinsoftheHPI,UTOPIA,

andGPIOperipherals.PCIfunctionalityforthesepinsiscontrolled(enabled/disabled)bythePCI_ENpin

(Y29).ThemaximumspeedofthePCI,33MHzor66MHz,iscontrolledthroughthePCI66pin(U27).For

moredetailedinformationontheperipheralcontrol,seeSection3,DeviceConfiguration.

TheC6455deviceprovidesaninitializationmechanismthroughwhichthedefaultvaluesforsomeofthe

PCIconfigurationregisterscanbereadfromanI2CEEPROM.Table7-98showstheregisterswhichcan

beinitializedthroughthePCIauto-initialization.Alsoshownisthedefaultvalueoftheseregisterswhen

PCIauto-initializationisnotused.PCIauto-initializationiscontrolled(enabled/disabled)throughthe

PCI_EEAIpin(P25).Formoreinformationonthisfeature,seetheTMS320C645xDSPPeripheral

ComponentInterconnect(PCI)User'sGuide(literaturenumberSPRUE60)andtheTMS320C645x

BootloaderUser'sGuide(literaturenumberSPRUEC6).

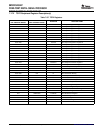

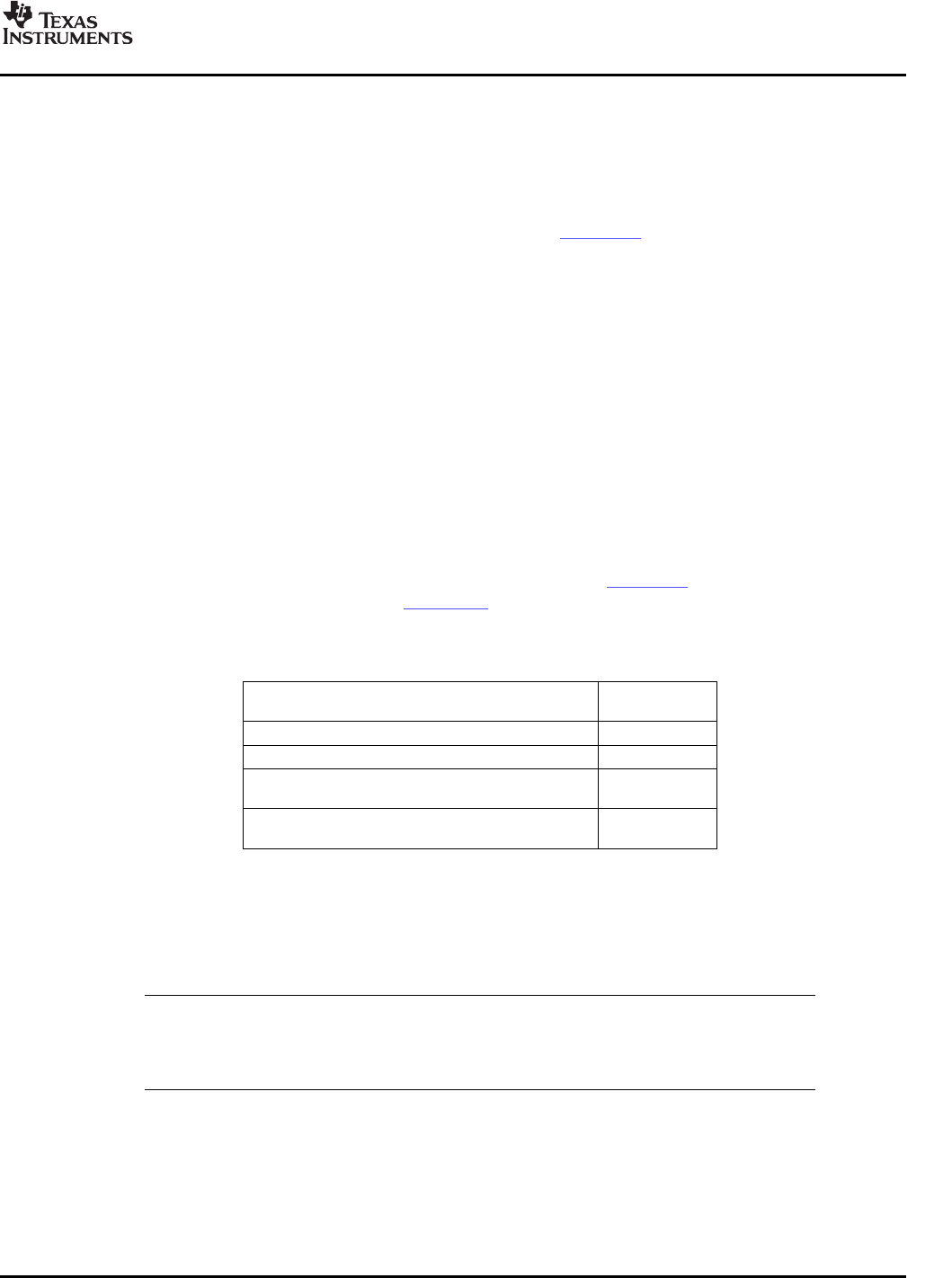

Table7-98.DefaultValuesforPCIConfiguration

Registers

DEFAULT

REGISTER

VALUE

VendorID/DeviceIDRegister(PCIVENDEV)104CB000h

ClassCode/RevisionIDRegister(PCICLREV)00000001h

SubsystemVendorID/SubsystemIDRegister00000000h

(PCISUBID)

MaxLatency/MinGrant/InterruptPin/InterruptLine00000100h

Register(PCILGINT)

Theon-chipBootloadersupportsahostbootwhichallowsanexternalPCIdevicetoloadapplicationcode

intotheDSP'smemoryspace.ThePCIbootisterminatedwhentheHostgeneratesaDSPinterrupt.The

HostcangenerateaDSPinterruptthroughthePCIperipheralbysettingtheDSPINTbitintheBack-End

ApplicationInterruptEnableSetRegister(PCIBINTSET)andtheStatusSetRegister(PCISTATSET).For

moreinformationonthebootsequenceoftheC6455DSP,seeSection2.4.

NOTE

Afterthehostbootiscomplete,theDSPinterruptisregisteredinbit0(channel0)ofthe

EDMAEventRegister(ER).Thiseventmustbeclearedbysoftwarebeforetriggering

transfersonDMAchannel0.

SubmitDocumentationFeedbackC64x+PeripheralInformationandElectricalSpecifications223