www.ti.com

4.4BusPriorities

SM320C6455-EP

FIXED-POINTDIGITALSIGNALPROCESSOR

SPRS462B–SEPTEMBER2007–REVISEDJANUARY2008

OntheC6455device,buspriorityisprogrammableforeachmaster.Theregisterbitfieldsanddefault

prioritylevelsforC6455busmastersareshowninTable4-2.Theprioritylevelsshouldbetunedtoobtain

thebestsystemperformanceforaparticularapplication.Lowervaluesindicatehigherpriorities.Forsome

masters,thepriorityvaluesareprogrammedatthesystemlevelbyconfiguringthePRI_ALLOCregister.

DetailsonthePRI_ALLOCregisterareshowninFigure4-3.TheC64x+megamodule,SRIO,andEDMA

masterscontainregistersthatcontroltheirownpriorityvalues.

Thepriorityisenforcedwhenseveralmastersinthesystemarevyingforthesameendpoint.Notethatthe

configurationSCRportonthedataSCRisconsideredasingleendpointmeaningprioritywillbeenforced

whenmultiplemasterstrytoaccesstheconfigurationSCR.Priorityisalsoenforcedontheconfiguration

SCRsidewhenamaster(throughthedataSCR)triestoaccessthesameendpointastheC64x+

megamodule.

InthePRI_ALLOCregister,theHOSTfieldappliestothepriorityoftheHPIandPCIperipherals.The

EMACfieldspecifiesthepriorityoftheEMACperipheral.TheSRIOfieldisusedtospecifythepriorityof

theSerialRapidIOwhenaccessingdescriptorsfromsystemmemory.ThepriorityforSerialRapidIOdata

accessesissetintheperipheralitself.

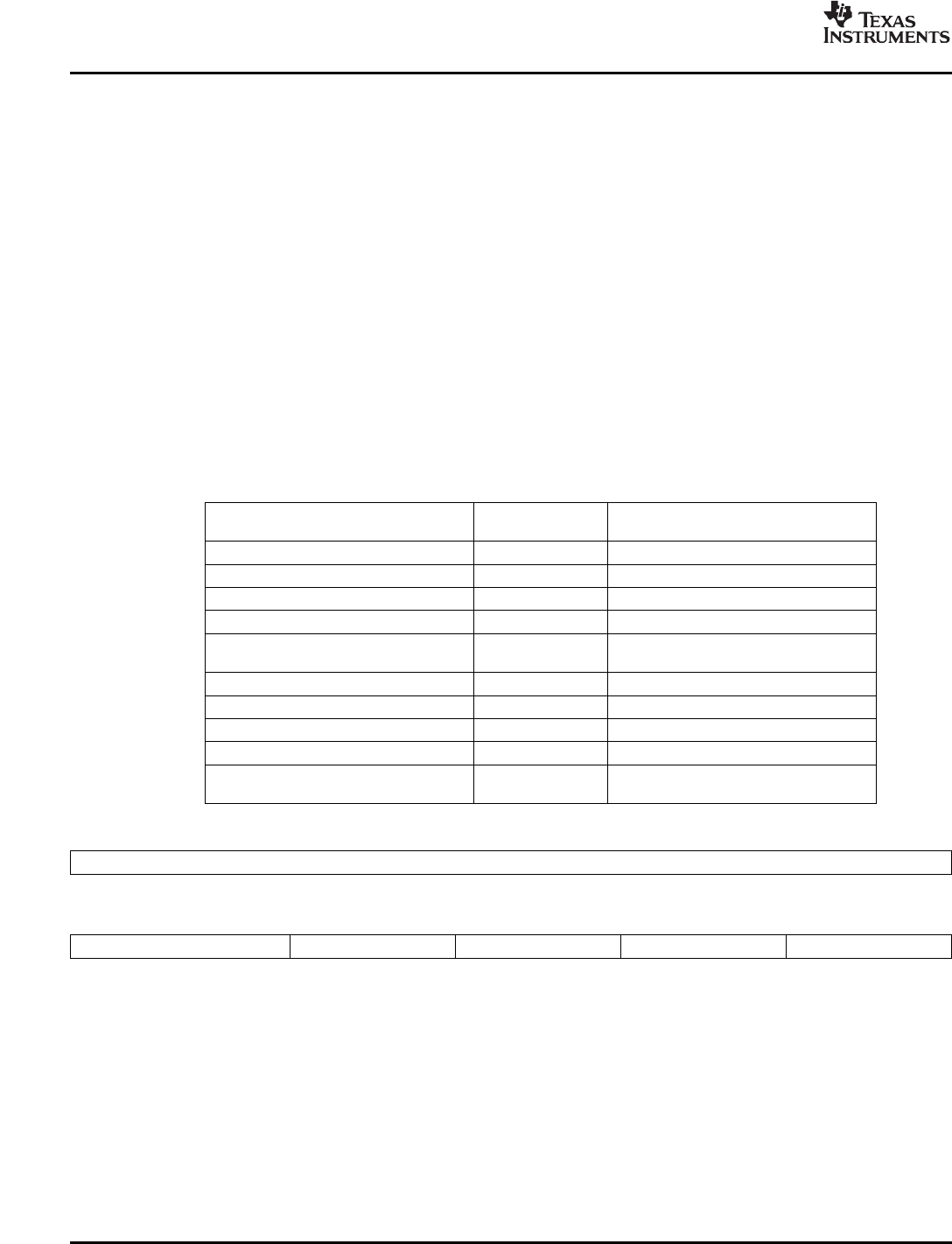

Table4-2.C6455DefaultBusMasterPriorities

DEFAULT

BUSMASTERPRIORITYCONTROL

PRIORITYLEVEL

EDMA3TC00QUEPRI.PRIQ0(EDMA3register)

EDMA3TC10QUEPRI.PRIQ1(EDMA3register)

EDMA3TC20QUEPRI.PRIQ2(EDMA3register)

EDMA3TC30QUEPRI.PRIQ3(EDMA3register)

SRIO(DataAccess)=0PER_SET_CNTL.CBA_TRANS_PRI

(SRIOregister)

SRIO(DescriptorAccess)0PRI_ALLOC.SRIO

EMAC1PRI_ALLOC.EMAC

PCI2PRI_ALLOC.HOST

HPI2PRI_ALLOC.HOST

C64x+Megamodule(MDMAport)7MDMAARBE.PRI(C64x+Megamodule

Register)

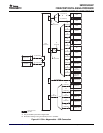

3116

Reserved

R-0000000000000000

1512119865320

ReservedSRIOReservedHOSTEMAC

R-0000R/W-001R-100R/W-010R/W-001

LEGEND:R/W=Read/Write;R=Readonly;-n=valueatreset

Figure4-3.PriorityAllocationRegister(PRI_ALLOC)

SystemInterconnect 86SubmitDocumentationFeedback