www.ti.com

7.17EnhancedTurboDecoderCoprocessor(TCP2)

7.17.1TCP2Device-SpecificInformation

SM320C6455-EP

FIXED-POINTDIGITALSIGNALPROCESSOR

SPRS462B–SEPTEMBER2007–REVISEDJANUARY2008

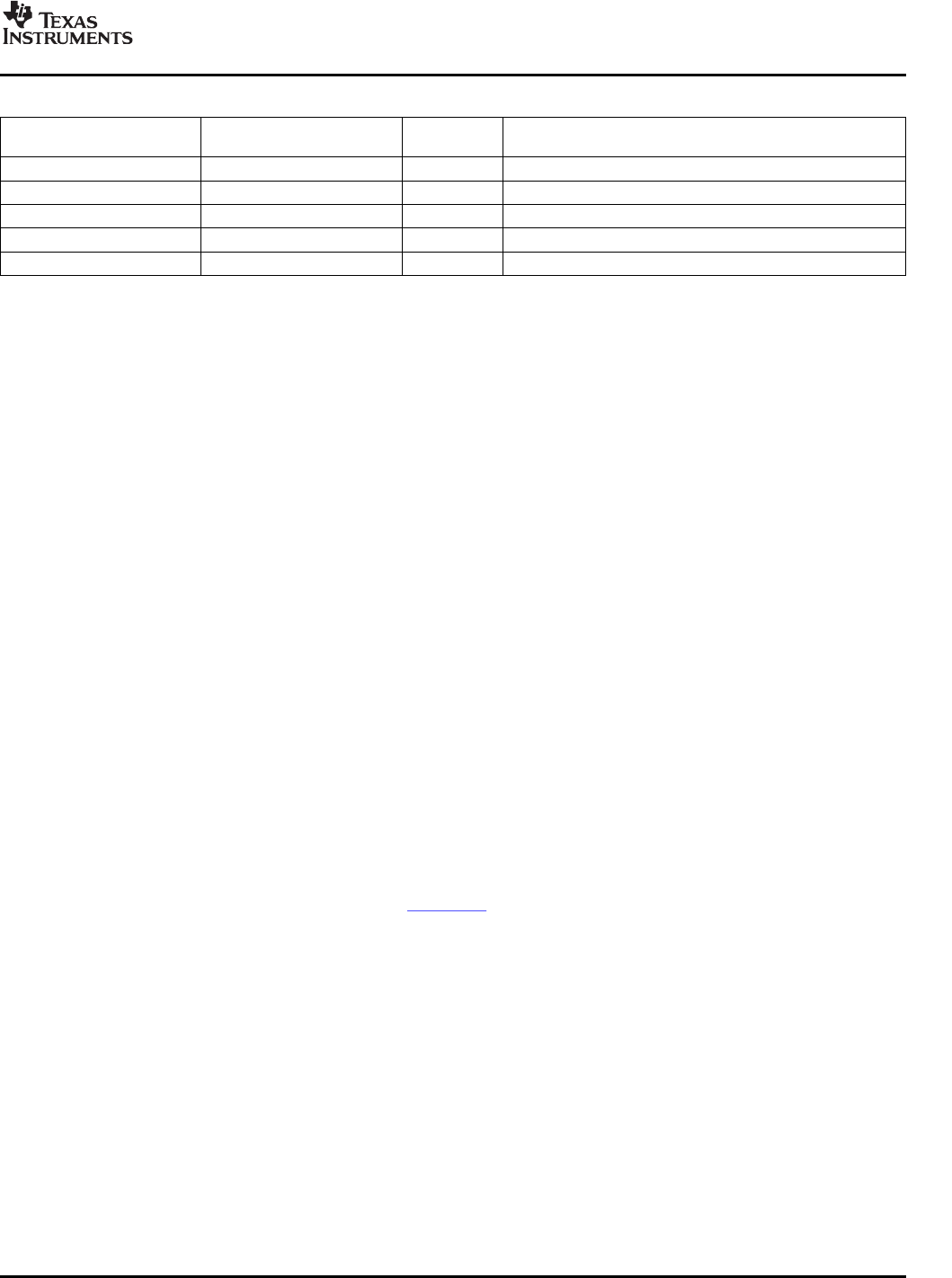

Table7-96.VCP2Registers(continued)

EDMABUSCONFIGURATIONBUS

ACRONYMREGISTERNAME

HEXADDRESSRANGEHEXADDRESSRANGE

58001000-BMBranchMetrics

58002000-SMStateMetric

58003000-TBHDTracebackHardDecision

58006000-TBSDTracebackSoftDecision

5800F000-IODecodedBits

TheC6455devicehasahigh-performanceembeddedcoprocessor[Turbo-DecoderCoprocessor(TCP2)

thatsignificantlyspeedsupchannel-decodingoperationson-chip.WiththeCPUoperatingat1GHz,the

TCP2candecodeuptoforty384-Kbpsoreight2-Mbpsturbo-encodedchannels(assuming8iterations).

TheTCP2implementsthemax*log-mapalgorithmandisdesignedtosupportallpolynomialsandrates

requiredbyThird-GenerationPartnershipProjects(3GPPand3GPP2),withfullyprogrammableframe

lengthandturbointerleaver.Decodingparameterssuchasthenumberofiterationsandstoppingcriteria

arealsoprogrammable.CommunicationsbetweentheTCP2andtheCPUarecarriedoutthroughthe

EDMA3controller.

TheTCP2supports:

•ParallelconcatenatedconvolutionalturbodecodingusingtheMAPalgorithm

•Allturbocoderatesgreaterthanorequalto1/5

•3GPPandCDMA2000turboencodertrellis

•3GPPandCDMA2000blocksizesinstandalonemode

•Largerblocksizesinsharedprocessingmode

•BothmaxlogMAPandlogMAPdecoding

•Slidingwindowsalgorithmwithvariablereliabilityandprologlengths

•Theprologreductionalgorithm

•Executionofaminimumandmaximumnumberofiterations

•TheSNRstoppingcriteriaalgorithm

•TheCRCstoppingcriteriaalgorithm

FormoredetailedinformationontheTCP2,seetheTMS320C645xDSPTurbo-DecoderCoprocessor2

(TCP2)ReferenceGuide(literaturenumberSPRU973).

SubmitDocumentationFeedbackC64x+PeripheralInformationandElectricalSpecifications221