www.ti.com

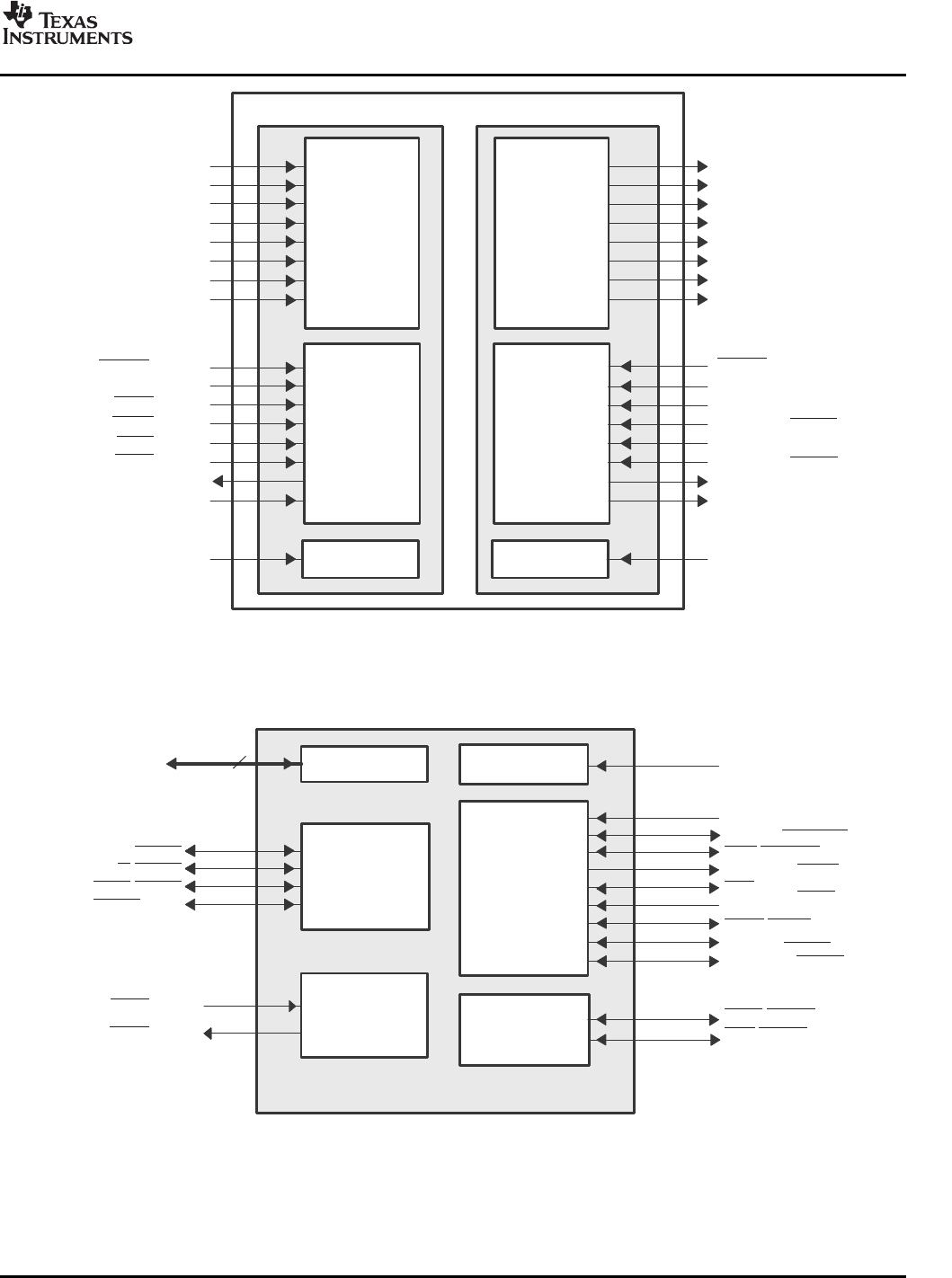

URADDR2/PINTA/GP[14]

Control/Status

URADDR4/PCLK/GP[2]

URDATA0/MRXD0/RMRXD0

URDATA1/MRXD1/RMRXD1

URADDR3/PREQ/GP[15]

URADDR1/PRST/GP[13]

URADDR0/PGNT/GP[12]

Receive

URDATA7/MRXD7

URDATA4/MRXD4

URDATA3/MRXD3

URDATA2/MRXD2

URCLAV/MCRS/RMCRSDV

URENB/MRXDV

URDATA5/MRXD5

URDATA6/MRXD6

URSOC/MRXER/RMRXER

URCLK/MRCLK

Clock

Control/Status

Transmit

Clock

UXADDR2/PCBE3

UXADDR4/GMDCLK

UXDATA0/MTXD0/RMTXD0

UXDATA1/MTXD1/RMTXD1

UXADDR3/GMDIO

UXADDR1/PIDSEL

UXADDR0/PTRDY

UXDATA7/MTXD7

UXDATA4/MTXD4

UXDATA3/MTXD3

UXDATA2/MTXD2

UXCLAV/GMTCLK

UXENB/MTXEN/RMTXEN

UXDATA5/MTXD5

UXDATA6/MTXD6

UXSOC/MCOL/TCLKRISE

UXCLK/MTCLK/REFCLK

UTOPIA (SLAVE)

(A)

A. These UTOPIA pins are muxed with the PCI or EMAC or GPIO peripherals. By default, these signals function as GPIO or EMAC peripheral

pins or have no function. For more details on these muxed pins, see the Device Configuration section of this data sheet.

HD[15:0]/AD[15:0]

HR/W/PCBE2

HDS2/PCBE1

UXADDR4/PCBE0/GP[2]

HHWIL/PCLK

HINT/PFRAME

URADDR2/PINTA/GP[14]

Data/Address

Arbitration

32

Clock

Control

PCI Interface

(A)

HAS/PPAR

URADDR1/PRST/GP[13]

HRDY/PIRDY

HCNTL0/PSTOP

UXADDR0/PTRDY

UXADDR2/PCBE3

UXADDR1/PIDSEL

HCNTL1/PDEVSEL

HDS1/PSERR

Error

Command

Byte Enable

HCS/PPERR

URADDR0/PGNT/GP[12]

URADDR3/PREQ/GP[15]

HD[31:16]/AD[31:16]

A. These PCI pins are muxed with the HPI or UTOPIA or GPIO peripherals. By default, these signals function as HPI or GPIO or EMAC. For more

details on these muxed pins, see the Device Configuration section of this document.

SM320C6455-EP

FIXED-POINTDIGITALSIGNALPROCESSOR

SPRS462B–SEPTEMBER2007–REVISEDJANUARY2008

Figure2-11.UTOPIAPeripheralSignals

Figure2-12.PCIPeripheralSignals

SubmitDocumentationFeedbackDeviceOverview29