www.ti.com

7.8.1PLL2ControllerDevice-SpecificInformation

7.8.1.1InternalClocksandMaximumOperatingFrequencies

7.8.1.2PLL2ControllerOperatingModes

SM320C6455-EP

FIXED-POINTDIGITALSIGNALPROCESSOR

SPRS462B–SEPTEMBER2007–REVISEDJANUARY2008

AsshowninFigure7-23,theoutputofPLL2,PLLOUT,isdividedby2anddirectlyfedtotheDDR2

memorycontroller.ThisclockisusedbytheDDR2memorycontrollertogenerateDDR2CLKOUTand

DDR2CLKOUT.Notethat,internally,thedatabusinterfaceoftheDDR2memorycontrollerisclockedby

SYSCLK2ofthePLL1controller.

ThePLLOUT/2clockisalsofedbackintothePLL2controllerwhereitbecomesSYSREFCLK.DividerD1

ofthePLL2controllergeneratesSYSCLK1fortheEthernetmediaaccesscontroller(EMAC).TheEMAC

usesSYSCLK1togeneratethenecessaryclockforeachofitsinterfaces.DividerD1shouldbe

programmedto÷2mode[default]whenusingtheGigabitMediaIndependentInterface(GMII)modeand

to÷5modewhenusingtheReduceGigabitMediaIndependentInterface(RGMII).DividerD1issoftware

programmableand,ifnecessary,mustbeprogrammedafterdeviceresetto÷5whentheRGMIImodeof

theEMACisused.Notethat,internally,thedatabusinterfaceoftheEMACisclockedbySYSCLK3ofthe

PLL2controller.

NotethatthereisaminimumandmaximumoperatingfrequencyforPLLREF,PLLOUT,andSYSCLK1.

Theclockgeneratormustnotbeconfiguredtoexceedanyoftheseconstraints.ForthePLLclocksinput

andoutputfrequencyranges,seeTable7-31.Also,whenEMACisenabledwithRGMIIorGMII,CLKIN2

mustbe25MHz.

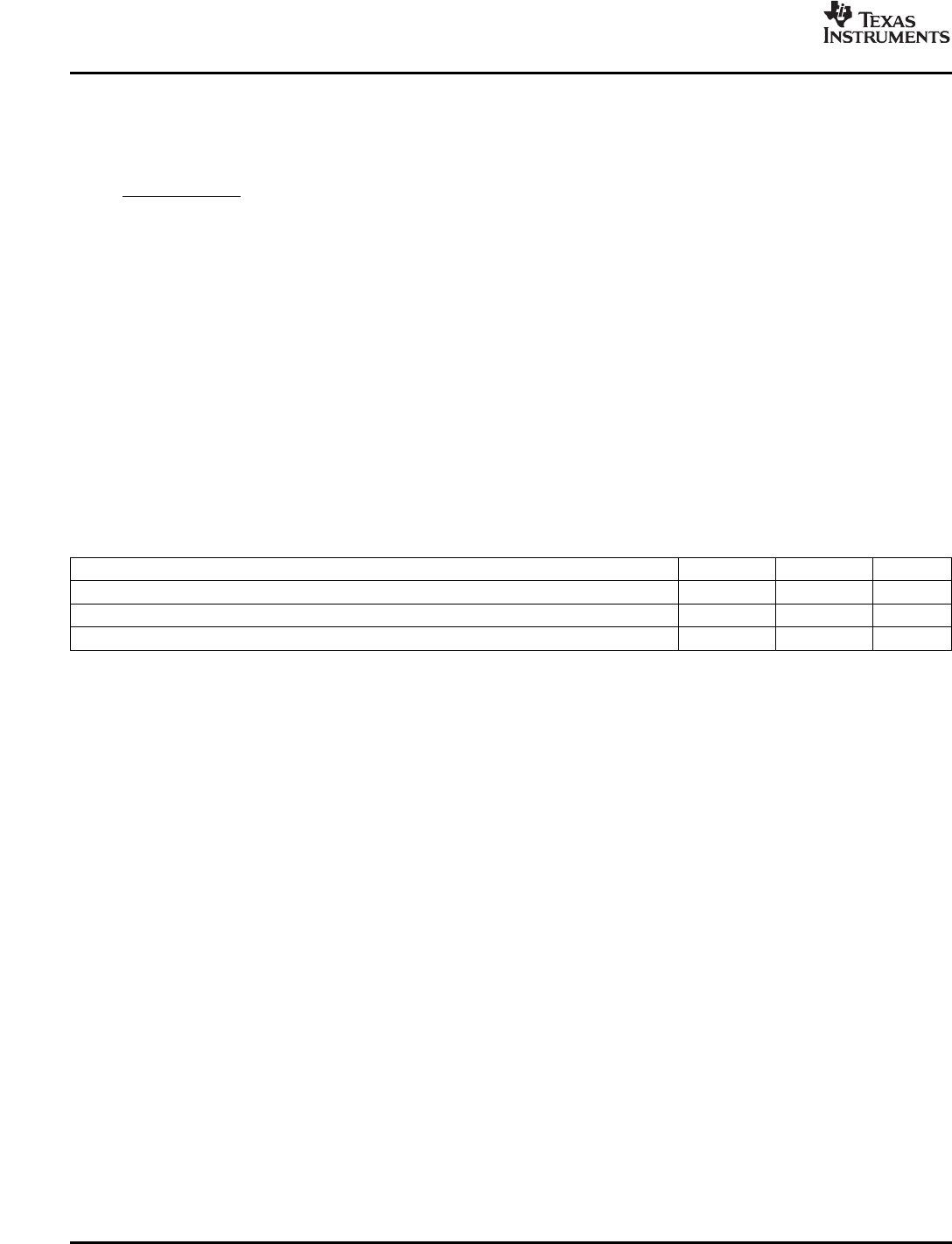

Table7-31.PLL2ClockFrequencyRanges

CLOCKSIGNALMINMAXUNIT

PLLREF(PLLEN=1)12.526.7MHz

PLLOUT250533MHz

SYSCLK1

(1)

50125MHz

(1)SYSCLK1restrictionappliesonlywhentheEMACisenabledandtheRGMIIorGMIImodesareused.SYSCLK1mustbeprogrammed

to125MHzwhentheGMIImodeisusedandto50MHzwhentheRGMIImodeisused.

UnlikethePLL1controllerwhichcanoperateinbypassandaPLLmode,thePLL2controlleronly

operatesinPLLmode.Inthismode,SYSREFCLKisgeneratedoutsidethePLL2controllerbydividingthe

outputofPLL2bytwo.

ThePLL2controllerisaffectedbypower-onreset,warmreset,andmaxreset.Duringtheseresetsthe

PLL2controllerregistersgetresettotheirdefaultvalues.TheinternalclocksofthePLL2controllerare

alsoaffectedasdescribedinSection7.6,ResetController.

PLL2isonlyunlockedduringthepower-upsequence(seeSection7.6,ResetController)andislockedby

thetimetheRESETSTATpingoeshigh.Itdoesnotloselockduringanyoftheotherresets.

C64x+PeripheralInformationandElectricalSpecifications 152SubmitDocumentationFeedback