www.ti.com

7.8.3.3PLLControllerStatusRegister

7.8.3.4PLLControllerClockAlignControlRegister

SM320C6455-EP

FIXED-POINTDIGITALSIGNALPROCESSOR

SPRS462B–SEPTEMBER2007–REVISEDJANUARY2008

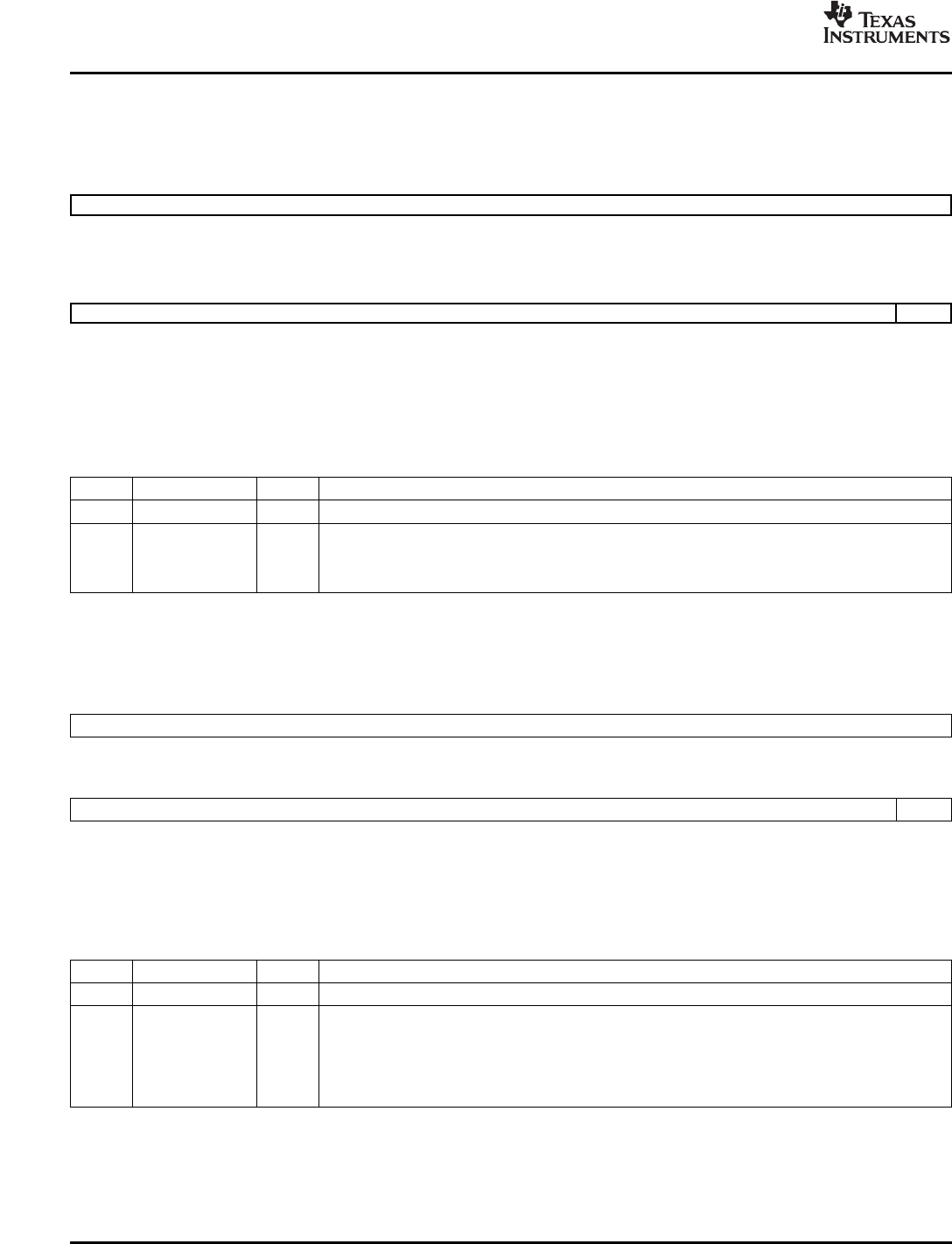

ThePLLcontrollerstatusregister(PLLSTAT)showsthePLLcontrollerstatus.PLLSTATisshownin

Figure7-26anddescribedinTable7-35.

3116

Reserved

R-0

1510

ReservedGOSTAT

R-0R-0

LEGEND:R/W=Read/Write;R=Readonly;-n=valueafterreset

Figure7-26.PLLControllerStatusRegister(PLLSTAT)[HexAddress:029C013C]

Table7-35.PLLControllerStatusRegister(PLLSTAT)FieldDescriptions

BitFieldValueDescription

31:1Reserved0Reserved.Thereservedbitlocationisalwaysreadas0.Avaluewrittentothisfieldhasnoeffect.

0GOSTATGOoperationstatus.

0Gooperationisnotinprogress.SYSCLKdivideratiosarenotbeingchanged.

1GOoperationisinprogress.SYSCLKdivideratiosarebeingchanged.

ThePLLcontrollerclockaligncontrolregister(ALNCTL)isshowninFigure7-27anddescribedin

Table7-36.

3116

Reserved

R-0

1510

ReservedALN1

R-0R/W-1

LEGEND:R/W=Read/Write;R=Readonly;-n=valueafterreset

Figure7-27.PLLControllerClockAlignControlRegister(ALNCTL)[HexAddress:029C0140]

Table7-36.PLLControllerClockAlignControlRegister(ALNCTL)FieldDescriptions

BitFieldValueDescription

31:1Reserved0Reserved.Thereservedbitlocationisalwaysreadas0.Avaluewrittentothisfieldhasnoeffect.

0ALN1SYSCLK1alignment.Donotchangethedefaultvaluesofthesefields.

0DonotalignSYSCLK1duringGOoperation.IfSYS1inDCHANGEissetto1,SYSCLK1switches

tothenewratioimmediatelyaftertheGOSETbitinPLLCMDisset.

1AlignSYSCLK1whentheGOSETbitinPLLCMDisset.TheSYSCLK1ratioissettotheratio

programmedintheRATIObitinPLLDIV1.

C64x+PeripheralInformationandElectricalSpecifications 156SubmitDocumentationFeedback