www.ti.com

RXD[3:0]

(A)

RXCTL

(A)

RXC

(at DSP)

(B)

5

RXERRRXDV

6

1st Half-byte

2nd Half-byte

RXD[7:4]RXD[3:0]

2

3

1

4

4

SM320C6455-EP

FIXED-POINTDIGITALSIGNALPROCESSOR

SPRS462B–SEPTEMBER2007–REVISEDJANUARY2008

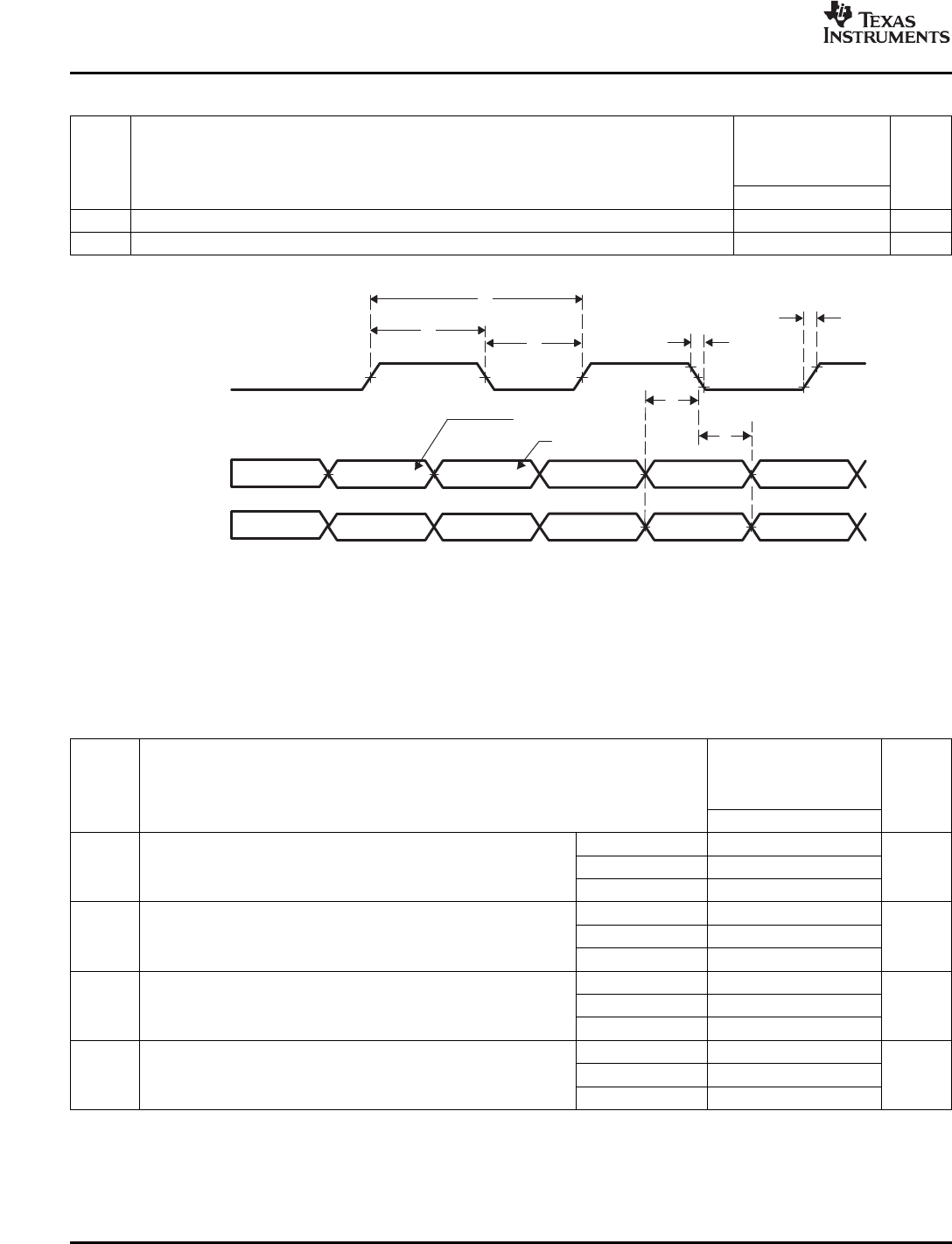

Table7-86.TimingRequirementsforEMACRGMIIInputReceivefor10/100/1000Mbps

(1)

(seeFigure7-69)

-720

-850

A-1000/-1000

NO.UNIT

-1200

MINMAX

5t

su(RXD-RXCH)

Setuptime,receiveselectedsignalsvalidbeforeRXC(atDSP)high/low1.0ns

6t

h(RXCH-RXD)

Holdtime,receiveselectedsignalsvalidafterRXC(atDSP)high/low1.0ns

(1)ForRGMII,receiveselectedsignalsinclude:RXD[3:0]andRXCTL.

A.Dataandcontrolinformationisreceivedusingbothedgesoftheclocks.RXD[3:0]carriesdatabits3-0ontherising

edgeofRXCanddatabits7-4onthefallingedgeofRXC.Similarly,RXCTLcarriesRXDVonrisingedgeofRXCand

RXERRonfallingedge

B.RXCmustbeexternallydelayedrelativetothedataandcontrolpins.

Figure7-69.EMACReceiveInterfaceTiming[RGMIIOperation]

(A)(B)

Table7-87.SwitchingCharacteristicsOverRecommendedOperatingConditionsforTXC-RGMII

Operationfor10/100/1000Mbit/s(seeFigure7-70)

-720

-850

A-1000/-1000

NO.UNIT

-1200

MINMAX

10Mbps360440

1t

c(TXC)

Cycletime,TXC100Mbps3644ns

1000Mbps7.28.8

10Mbps0.40*t

c(TXC)

0.60*t

c(TXC)

2t

w(TXCH)

Pulseduration,TXChigh100Mbps0.40*t

c(TXC)

0.60*t

c(TXC)

ns

1000Mbps0.45*t

c(TXC)

0.55*t

c(TXC)

10Mbps0.40*t

c(TXC)

0.60*t

c(TXC)

3t

w(TXCL)

Pulseduration,TXClow100Mbps0.40*t

c(TXC)

0.60*t

c(TXC)

ns

1000Mbps0.45*t

c(TXC)

0.55*t

c(TXC)

10Mbps0.75

4t

t(TXC)

Transitiontime,TXC100Mbps0.75ns

1000Mbps0.75

C64x+PeripheralInformationandElectricalSpecifications 214SubmitDocumentationFeedback