www.ti.com

SM320C6455-EP

FIXED-POINTDIGITALSIGNALPROCESSOR

SPRS462B–SEPTEMBER2007–REVISEDJANUARY2008

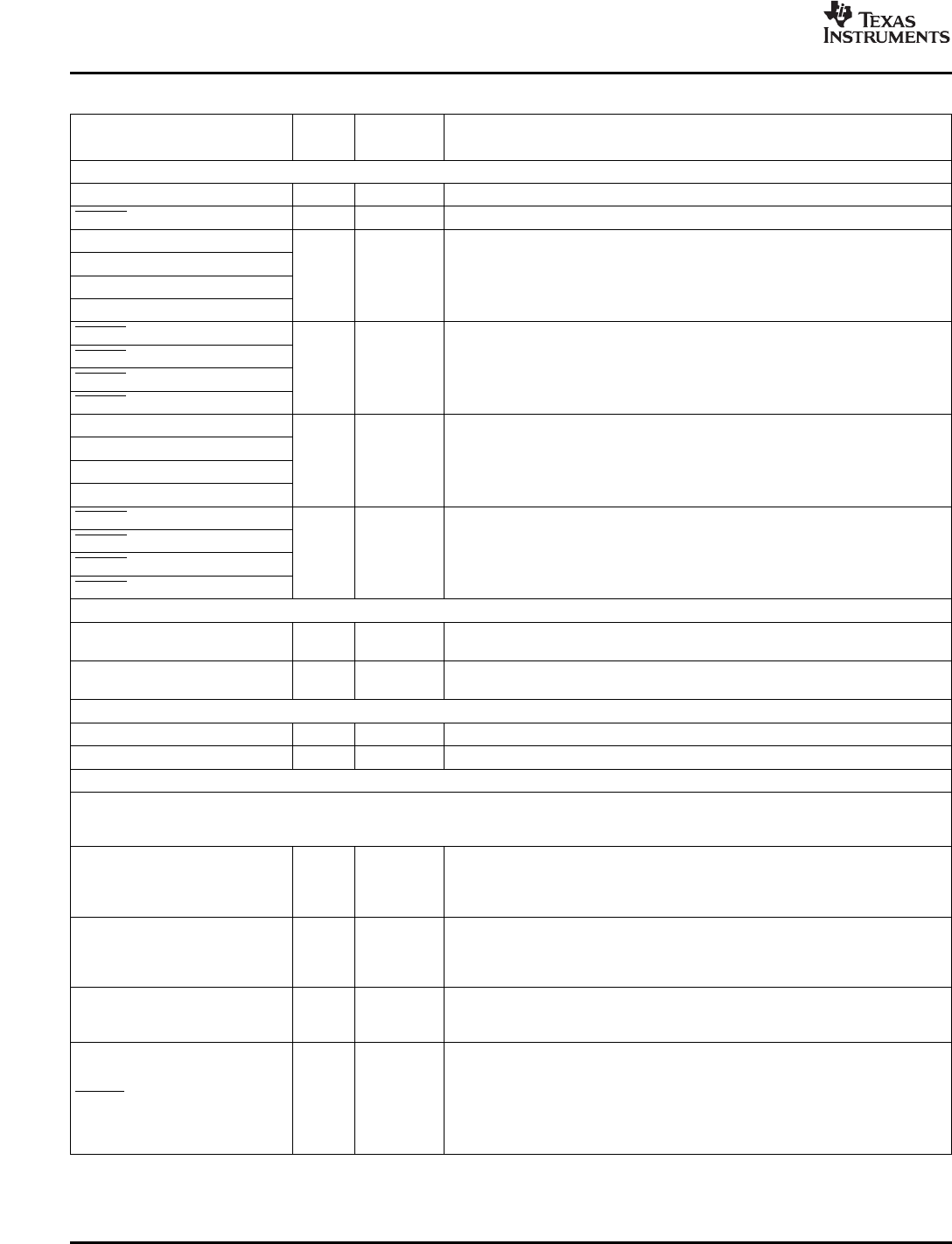

Table2-3.TerminalFunctions(continued)

SIGNAL

TYPE

(1)

IPD/IPU

(2)

DESCRIPTION

NAMENO.

RAPIDIOSERIALPORT

RIOCLKAF15IRapidIOserialportsource(reference)clock

RIOCLKAG15INegativeRapidIOserialportsource(reference)clock

RIOTX3AF17

RIOTX2AG18

O/ZRapidIOtransmitdatabusbits[3:0](differential)

RIOTX1AG22

RIOTX0AF23

RIOTX3AF18

RIOTX2AG19

O/ZRapidIOnegativetransmitdatabusbits[3:0](differential)

RIOTX1AG21

RIOTX0AF22

RIORX3AH18

RIORX2AJ18

IRapidIOreceivedatabusbits[3:0](differential)

RIORX1AJ22

RIORX0AH22

RIORX3AH17

RIORX2AJ19

IRapidIOnegativereceivedatabusbits[3:0](differential)

RIORX1AJ21

RIORX0AH23

MANAGEMENTDATAINPUT/OUTPUT(MDIO)FORMII/RMII/GMII

UTOPIAtransmitaddresspin(UXADDR4)(I)4orMDIOserialclock(MDCLK)

UXADDR4/MDCLKM5I/O/ZIPD

forMII/RMII/RGMIImode(O)

UTOPIAtransmitaddresspin3(UXADDR3)(I)orMDIOserialdata(MDIO)for

UXADDR3/MDION3I/O/ZIPU

MII/RMII/RGMIImode(I/O)

MANAGEMENTDATAINPUT/OUTPUT(MDIO)FORRGMII

RGMDCLKB4O/ZMDIOserialclock(RGMIImode)(RGMDCLK)(O)

RGMDIOA4I/O/ZMDIOserialdata(RGMIImode)(RGMDIO)(I/O)

ETHERNETMAC(EMAC)[MII/RMII/GMII]

IftheEthernetMAC(EMAC)andMDIOareenabled(AEA12drivenlow[UTOPIA_EN=0]),therearetwoadditionalconfigurationpins—

theMAC_SEL[1:0](AEA[10:9]pins)thatselectoneofthefourinterfacemodes(MII,RMII,GMII,orRGMII)fortheEMAC/MDIOinterface.

FormoredetailedinformationontheEMACconfigurationpins,seeSection3,DeviceConfiguration.

UTOPIAreceiveclock(URCLK)drivenbyMasterATMController(I)orwhen

theUTOPIAperipheralisdisabled(UTOPIA_EN[AEA12pin]=0),thispinis

URCLK/MRCLKH1I

EMACreceiveclock(MRCLK)forMII[default]orGMII.MACSEL[1:0]

dependent.

UTOPIAreceivecellavailablestatusoutputsignalfromUTOPIASlave(O)or

URCLAV/MCRS/whentheUTOPIAperipheralisdisabled(UTOPIA_EN[AEA12pin]=0),this

J4I/O/Z

RMCRSDVpinisEMACcarriersense(MCRS)(I)forMII[default]orGMII,orEMACcarrier

sense/receivedatavalid(RMCRSDV)(I)forRMII.MACSEL[1:0]dependent.

UTOPIAreceiveStart-of-Cellsignal(I)orwhentheUTOPIAperipheralis

URSOC/MRXER/

H4Idisabled(UTOPIA_EN[AEA12pin]=0),thispinisEMACreceiveerror

RMRXER

(MRXIR)(I)forMII[default],RMII,orGMII.MACSEL[1:0]dependent.

UTOPIAreceiveinterfaceenableinputsignal(I).AssertedbytheMasterATM

ControllertoindicatetotheUTOPIASlavetosampletheReceiveDataBus

(URDATA[7:0])andURSOCsignalinthenextclockcycleorthereafter.

URENB/MRXDVH5I

WhentheUTOPIAperipheralisdisabled(UTOPIA_EN[AEA12pin]=0),this

pinisEMACMII[default]orGMIIreceivedatavalid(MRXDV)(I).MACSEL[1:0]

dependent.

DeviceOverview 42SubmitDocumentationFeedback