www.ti.com

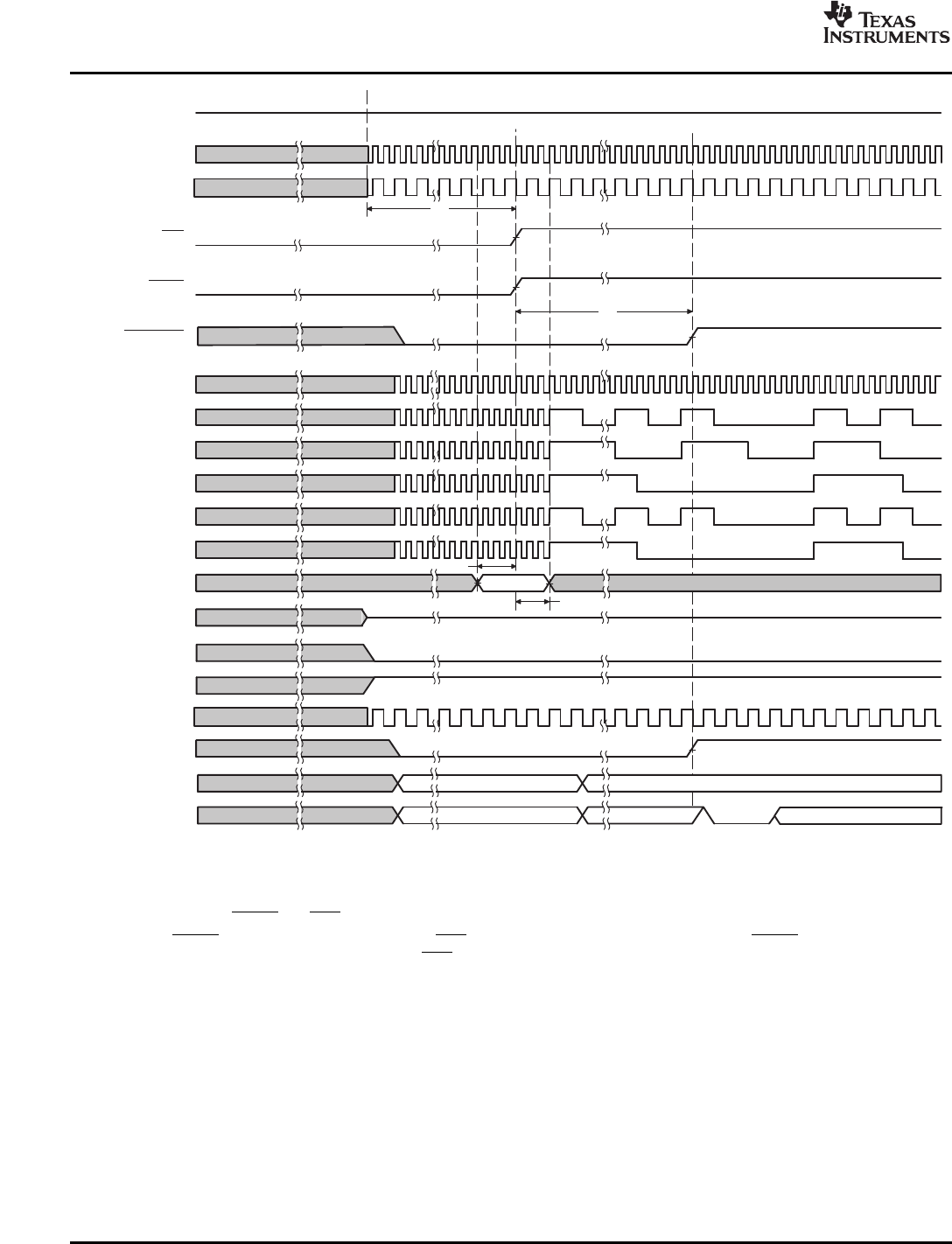

CLKIN1

PCLK

RESET

RESETSTAT

SYSREFCLK (PLL1C)

Z Group

POR

SYSCLK3

SYSCLK4

SYSCLK5

AECLKOUT (Internal)

Boot and Device

Configuration Pins

Low Group

High Group

CLKIN2

Internal Reset PLL2C

SYSREFCLK (PLL2C)

SYSCLK1 (PLL2C)

SYSCLK2

5

9

7

8

Undefined

Undefined

Low

High-Z

Undefined

High

PLL2 Unlocked

PLL2 Locked

(A)

PLL2 Unlocked

Clock Valid

Undefined

Undefined

Undefined

Clock Valid

(B)

Power Supplies Ramping Power Supplies Stable

SM320C6455-EP

FIXED-POINTDIGITALSIGNALPROCESSOR

SPRS462B–SEPTEMBER2007–REVISEDJANUARY2008

A.SYSREFCLKofthePLL2controllerrunsatCLKIN2×10.

B.SYSCLK1ofPLL2controllerrunsatSYSREFCLK/2(default).

C.Powersupplies,CLKIN1,CLKIN2(ifused),andPCLK(ifused)mustbestablebeforethestartoft

w(POR)

.

D.DonottietheRESETandPORpinstogether.

E.TheRESETpincanbebroughthighafterthePORpinhasbeenbroughthigh.Inthiscase,theRESETpinmustbe

heldlowforaminimumoft

w(RESET)

afterthePORpinhasbeenbroughthigh.

Figure7-8.Power-UpTiming

C64x+PeripheralInformationandElectricalSpecifications 134SubmitDocumentationFeedback